在高速 IC 设计过程中,信号完整性(SI)分析—特别是串扰噪声与延迟分析—是确保电路高质量和可靠性不可或缺的步骤。

1、为什么信号完整性分析如此关键?

信号完整性分析确保信号在芯片内部不遭失真、无误传播,直接影响 IC 的性能、功能与可靠性。串扰噪声(crosstalk noise)和串扰延迟(crosstalk delay)是两个主要挑战:

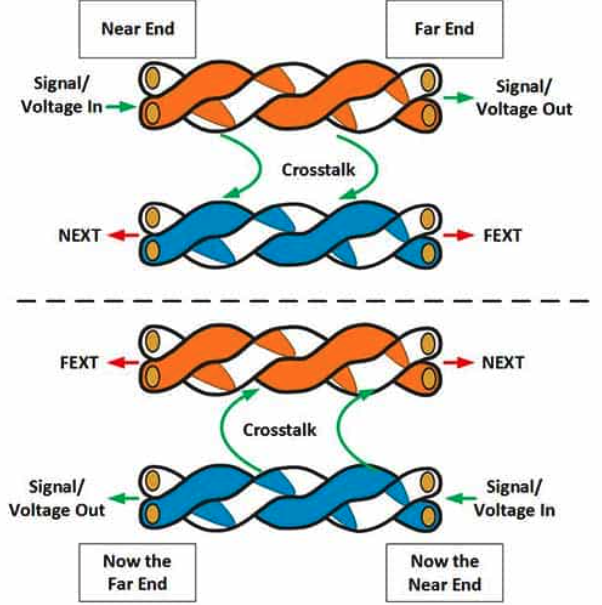

串扰噪声:当“施加路径”(aggressor)线路切换时,耦合会在相邻“受害路径”(victim)中引入干扰,可能导致逻辑错误或功能抖动。

串扰延迟:串扰效应不仅仅是噪声,还会加快或放慢信号,造成时序违规,破坏时序闭合。

深入 SI 分析帮助我们精准定位问题、修复错误,为后续设计阶段提供坚实基础。

2、四大关键技术与工具详解

I. 串扰噪声分析(Crosstalk Noise Analysis)

Case Study

某半导体公司在 post-route 阶段使用 Cadence CeltIC 工具分析串扰噪声,检测并修复因串扰导致的 glitch 与 delay 违规问题,并生成 buffer 插入、网间距调整等修复文件,显著提升设计质量。

实现策略:

使用 CeltIC 等工具进行细粒度噪声分析。

采用缓冲器插入、信号网隔离、屏蔽等修复策略减少串扰干扰。

II. 串扰延迟分析(Crosstalk Delay Analysis)

Case Study

某设计团队采用 Synopsys PrimeTime-SI 工具,将其整合进静态时序分析流程,以准确评估串扰引发的延迟变动,保证在模块级及全芯片级都满足时序要求。

实施建议:

在静态时序分析中纳入串扰延迟分析路径。

使用 PrimeTime-SI 等工具,生成包含串扰影响的 SDF 文件进行闭环验证。

III. 分层 SI 分析(Hierarchical SI Analysis)

实践方式

大型 SoC 设计中,将 SI 分析任务按模块—子模块分层进行,在保证精度的同时大幅提升验证效率。常见做法是利用工具生成每个 block 的抽象模型,再用于顶层 SI 验证。

优势:

支撑复杂系统级分析;

在早期获得模块性能反馈,降低整体验证负担。

IV. 物理感知 SI 分析(Physically Aware SI Analysis)

特点

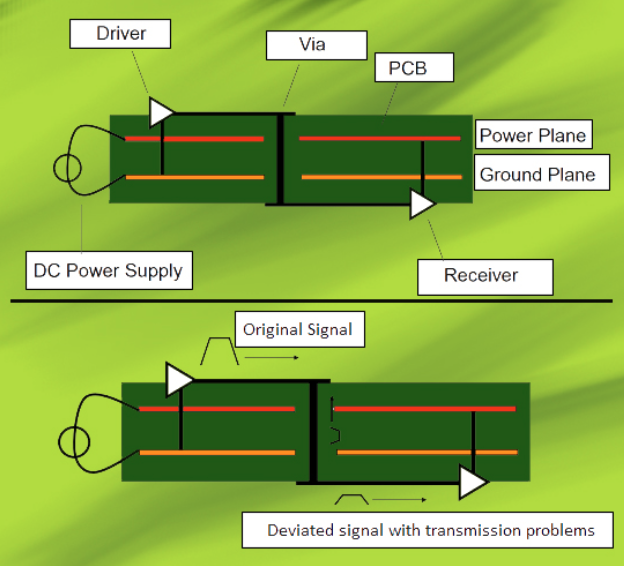

将物理布图信息(placement/routing)纳入 SI 分析,引入布局耦合、走线密度等物理因素,显著提升噪声与延迟预测的准确性。

工具支持:

Synopsys Hercules 等工具支持将物理约束直接集成进 SI 分析流程,从而优化电源分配与信号清晰度。

3、战略意义与核心优势一览

技术方向 优势摘要

串扰噪声分析 精确检测 glitch / 毫伏级干扰,避免功能异常

串扰延迟分析 保证时序精度,防止时序违例

分层 SI 分析 提高复杂 SoC 验证效率,模块级反馈快

物理感知 SI 分析 更贴合物理实现,提升时序精度与整体性能保障

融合这些先进技术,帮助 IC 设计人员全方位提升信号完整性验证能力,缩短开发周期,降低返工成本。

4、学习加速:EDA Academy 助你成为 SI 专业高手

若你希望系统掌握 SI 分析与优化前沿方法,EDA Academy(www.eda-academy.com) 是你的最佳选择:

拥有 海量、专业、全面、最新 的网课,覆盖串扰噪声、延迟分析、分层方法与物理感知分析等主题;

注册为导师,传授你自己的经验与知识,成为课程设计者;

用邮箱即可 免费订阅其 newsletter,定期获取最新热点与干货;

加入 销售联盟计划,推荐课程即可获得 20%–50% 的佣金,让学习更具收益价值。

5、从技术到平台,共筑 SI 精英之路

从串扰噪声、延迟分析,到分层与物理感知 SI 方法,再到 EDA Academy 的学习与成长通道,本文为你铺就一条完整的专业进阶路径。掌握先进 SI 技术,将极助你成为高质量 IC 设计的可靠守护者;加入 EDA Academy,开启你的职场“加速器”。