24V转12V降压电路设计 说明书

Part1.原理图设计

-

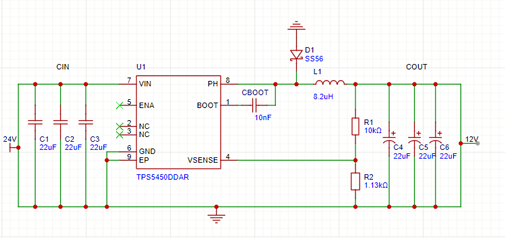

初步方案:

被组长指出没有好好读芯片手册+电源和地短接了。丑完了😢

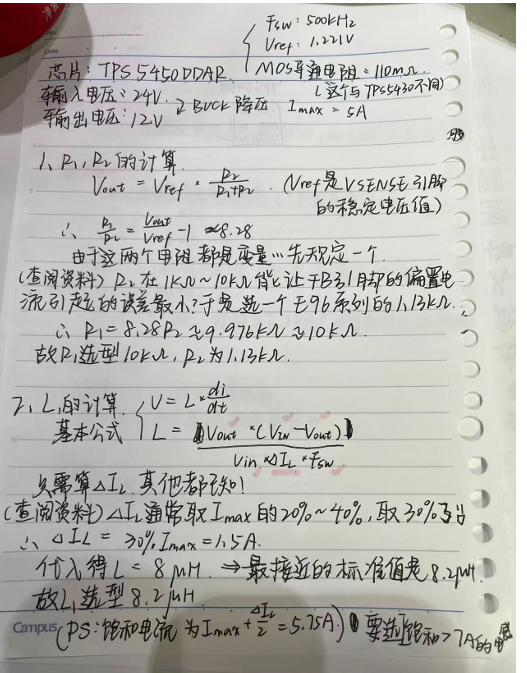

这是一些基本量的计算和推导,下面这些推导基本没问题

这个电路连接是非常错误的,被组长处刑了,疯狂算数据结果不会连电路...继续阅读芯片手册,接下来我进行了修改:

-

第二版:升级了梯度滤波电容,修改了短路和接地的问题,设置了ENA引脚的欠压锁定

-

梯度滤波电容(学长培训教的,可以滤各个波段,小的往后放)

-

输入滤波取值:

- 22\(\mu F\) 中频去耦

- 10\(\mu F\) 高频去耦

- 100\(\mu F\) 低频储能滤波

-

输出滤波取值:

- 22\(\mu F\) 主滤波电容

- 1\(\mu F\) 高频滤波

- 0.1 \(\mu F\) 特高频去耦

-

-

接地和电源

参考了芯片手册

-

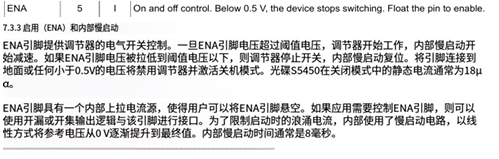

ENA引脚的配置

芯片手册中关于ENA引脚的规定(被我网页翻译了):

然后我们发现一些关于ENA引脚的参数

其中:

- 启动阈值电压1.3V

- 停止阈值电压0.5V

- 迟滞电压450mV:启动阈值与停止阈值之间的差值,防止电压在临界点抖动

这个时候就可以设计一个欠压锁定电路了!我的想法是当输入电压大于24V的时候芯片才被启动。

现在我们知道了输入电压\(V_{s}\) ,启动阈值电压 \(V_{ena}\) 。需要计算上下拉电阻 \(R_{up}\) 和 \(R_{down}\)

电阻分压:

\[V_{s}=V_{ena}*(1+\frac{R_{up}}{R_{down}}) \]现在又到了赋值环节,我简单将 \(R_{down}\) 设定为10 \(k \Omega\) 。求得\(R_{up}\) ≈174k\(\Omega\) 。

-

验算一下:

当\(V_{s}\) 为24V的时候,ENA引脚电压=24V*\(\frac{10k\Omega}{174k\Omega+10k\Omega}\) 约等于1.304V>\(V_{ena}\) ,哟西,够了。

差不多了。我这个原理图大概没问题了吧!(瘫)

-

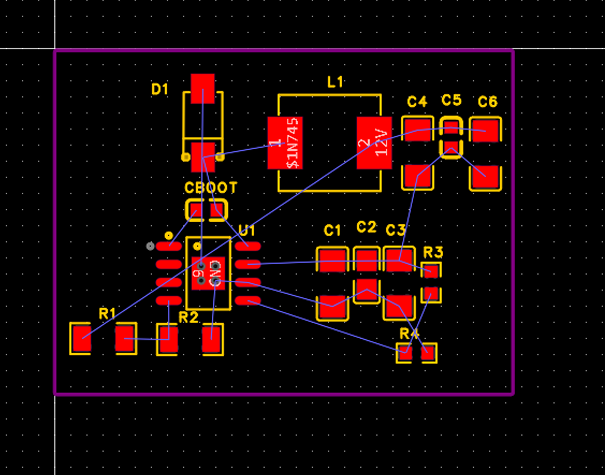

Part 2.PCB设计

-

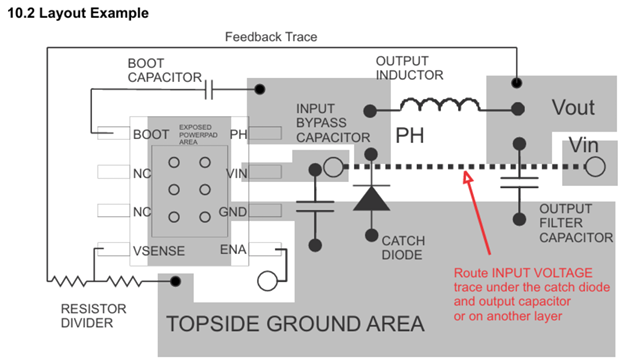

PCB布局

参考了一下芯片手册上的布局

我的布局是这样的:(R3和R4不知道放哪里...?)

然后按照芯片手册连线,变成了这样:

emmm我也不知道这个设计的咋样qwq,DRC没问题。