STM32主控芯片硬件设计总结

我记的有点过于多了。。。

因为想多学一点所以弄了这么多字的笔记,重要的会加粗标注的。

-

晶振电路设计

-

通常情况下,STM32芯片的原理图会使用两个晶振,而在进行晶振贴片时,由于晶振的体积比四周的电阻体积大很多,晶振会占用较多的空间。这对我们制作一些超小型电路板是不利的,因为板子空间有限。

-

低速晶振与高速晶振的区别

-

低速晶振(32.768kHz):

连接LSE,最终到达RTC。

对于掉电后不需要记录系统时间的电路板,我们将低速晶振舍去。

-

高速晶振(8MHz):

连接HSE,最终到达 SYSCLK。

SYSCLK是系统时钟,不可缺少。

对于STM32电路板,外部高速晶振需要保留,为芯片提供系统时钟。

-

-

晶振的起振电容(负载电容)

-

定义:

晶振的两条引线连接 IC 块内部及外部所有有效电容之和

-

意义:

晶振的标称值在测试时有一个“负载电容”的条件,在工作时满足这个条件,振荡频率才与标称值一致。

它只用于保持固定的电压值,不起其他的作用。

-

性质:

负载频率不同决定振荡器的振荡频率不同。标称频率相同的晶振,负载电容不一定相同。

-

-

晶振两端的电阻电容

-

电容(匹配电容):

只有在外部所接电容为匹配电容的情况下,振荡频率才能保证在标称频率附近的误差范围内。

一般大小为 30pF 左右

可以调整这两个电容的大小来微调振荡频率,可调范围在 10ppm 量级

-

常见问题:

-

晶振出现有时振有时不振:

晶振负载与两端电容不匹配

-

晶振本身有问题:

有寄生电容、阻抗值波动大、内部焊点不牢。

-

晶振装在板上不行,用电热风吹一下、拆下来重装就好了:

晶振负载与两端电容不匹配造成频率偏差太大,电热风实际改变了电路的杂散电容

-

晶振负载与晶振两端的电容的匹配:

\[C_{L}=\frac{C_{1}*C_{2}}{C_{1}+C_{2}+C^{''}} \]其中\(C_{L}\) 是晶振的负载电容值,$$C_{1}、C_{2}$$ 是晶振两端的电容值,\(C^{''}\) 是线路杂散电容。

-

-

-

-

复位电路设计

-

用处:

初始化每个寄存器,包括PC指针,不包括RAM,单片机从复位地址开始执行程序。

我的理解是指针全部偏移到初始位置,复原除了地址之外的所以值,因为地址是不能重复分配的。

-

准备:

-

复位信号:

每一种复位方式对应一种信号。

- 硬件复位:复位管脚低电平电压需要小于0.8V,输入脉冲时间为100ns。所以只需要在NRST管脚给小于0.8V的电压,持续时间为100ns就可以b实现复位

-

CPU正常工作、电源正常工作

-

-

设计:

-

RC充电电路:

电荷在极板上聚集的过程叫做瞬态过程。

一开始,电荷聚集的速度很快,导致电压急剧增加,但是速率变慢。

-

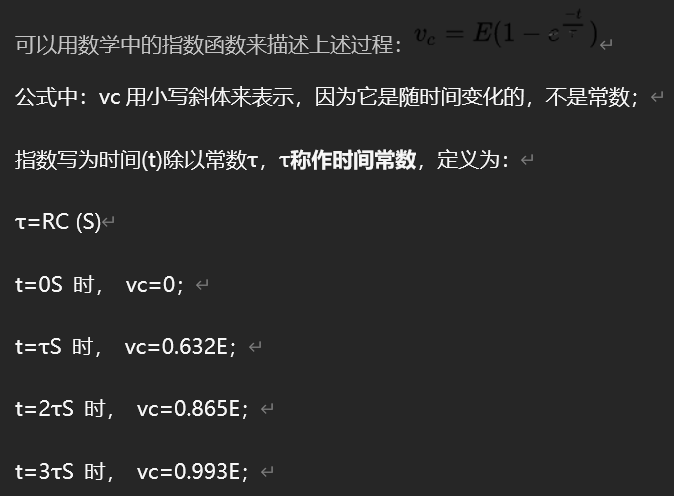

用指数函数来表示:

-

更进一步的来说,电容的大小反映了电容电压的变化的程度。电容越大,时间常数越大。

-

STM32单片机复位电路设计

-

原理:

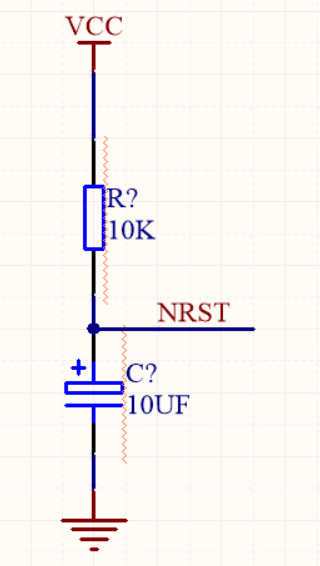

我们可以根据上述的RC充电原理,参考一个电阻和电容串联,中间段连接至STM32复位管脚。

为了保证复位的时间很短,当在一个时间常数时,电压为电源电压的0.632倍,若\(V_{CC}=3.3V\) 那么一个时间常数的电压为1.21V,不满足我们的需求,2个时间常数时为0.462V,满足要求。

时间为100ms,2RC=20ms,RC=10ms,可以选择R=10K,C=10uF

-

原理图电路设计:

刚接上电的时候,电路为低电平,这个时候单片机复位。

一个时间常数之后,NRST为高电平。之后一直保持高电平。

没错就是这个最简单的小电路,还有挺多小学问嘞。

-

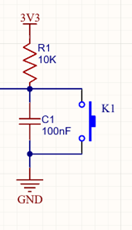

手动复位

手动复位也很简单,加入一个按钮,按键按下时NRST为低电平,此时复位。

-

-

-

-

启动模式选择以及下载调试电路

-

SMT32的存储器类型

-

组织架构:

程序存储器、数据存储器、寄存器、I/O端口排列在同意顺序的4GB地址空间内。

-

嵌入式Flash(闪存):

Flash接口:

-

可管理CPU通过AHB I-Code和D-Code对Flash进行访问

-

可针对Flash执行擦除和编程操作,并实施读写保护机制。

Flash结构:

-

主存储块

-

系统存储器

-

512字节OTP(一次性可编程)

-

选项字节

嵌入式SRAM:

STM32F405xx/07xx 和 STM32F415xx/17xx 带有 4 KB 备份 SRAM和 192 KB 系统 SRAM 。

-

-

-

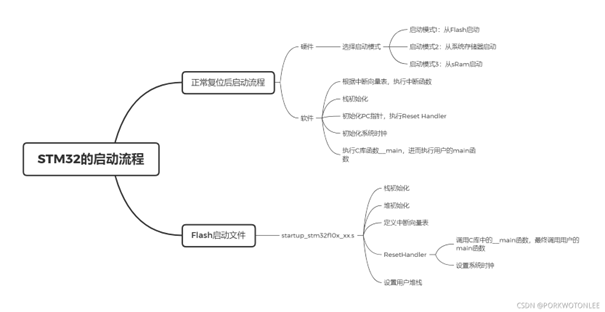

STM32的启动

-

启动流程:

-

硬件选择启动模式

-

读取启动模式对应的存储器的中断向量表

-

初始化栈

-

初始化PC指针,指向 Reset_hander

-

初始化系统时钟

-

执行C库函数main

-

-

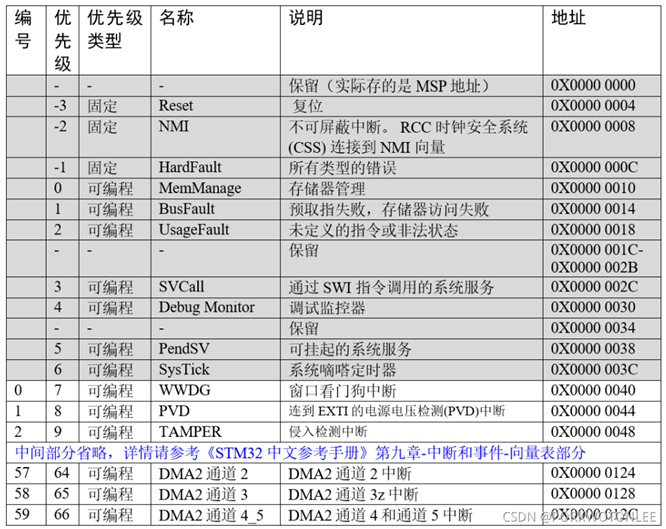

什么是中断向量表?

中断向量表本质上是一个32位整数数组,当他存储了发生异常时需要执行对应任务函数的地址,当发生异常情况时,会将对应的地址幅值给PC寄存器,进而执行任务。

-

-

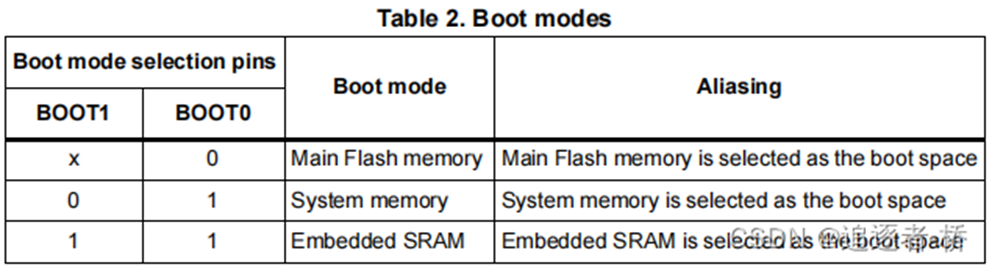

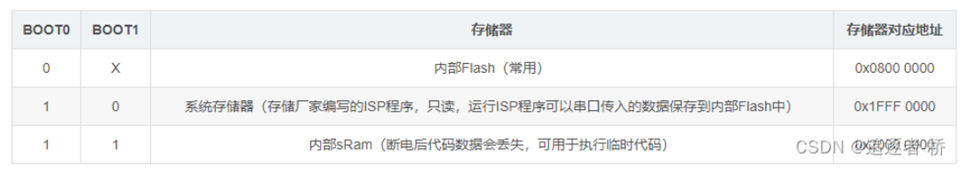

BOOT引脚的配置

可以通过BOOT引脚选择三种不同的启动模式,

-

如何配置:

在MCU复位后,在SYSCLK的第四个上升沿锁存BOOT引脚值。复位后,通过设置BOOT1和BOOT0引脚来选择启动方式。

-

BOOT的启动方式:

-

当设置 BOOT0=0的时候,系统会选择Flash的主存储块作为启动空间。

这意味着起始地址为0x0800 0000,复位之后PC指针也指向此处。

-

Flash锁死的调试方法:

- 可以调整BOOT引脚的配置(从系统存储器、SRAM启动)

- 重新烧录程序

-

当设置BOOT0=1,BOOT1=0时,选择系统存储器作为启动空间,即中断向量表定位于Flash的系统存储区域

这意味着起始(中断入口)地址:0x1FFF 0000

通常使用这种启动方式来实现串口下载程序,BootLoader负责下载程序的时候对芯片内部的Flash进行擦除于编写。在使用ISP下载完程序后需要将启动方式重新调整为Flash启动模式(即将BOOT0=0)

-

当设置BOOT0=1,BOOT1=1时,选择嵌入式SRAM(静态随机存储器)作为启动空间,即中断向量表定位于系统SRAM存储区域。

这意味着起始地址为0x2000 0000,复位之后PC指针也指向此处。

一般是编写一些小程序用来扫描所有的I/O口,然后再上测试信号,借此检测所有焊接是否正常,这样不必触动Flash中的程序。

-

-

-

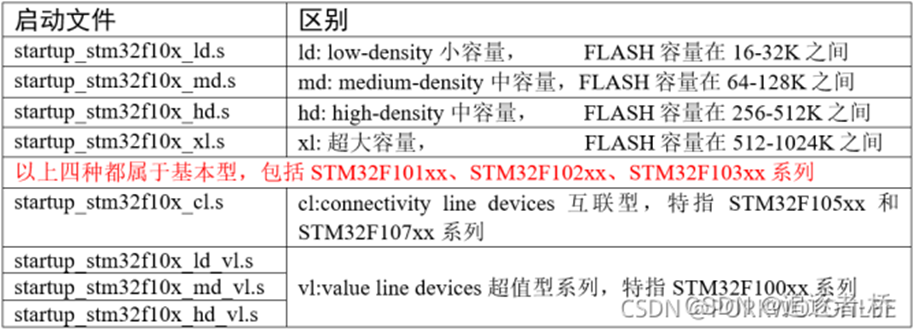

启动软件配置

-

F10系列启动文件:

-

启动文件内容:

-

初始化堆

-

初始化栈

-

配置中断处理函数Reset_Handler

-

配置系统时钟

-

通过C/C++标准实时库的_main函数,跳转到.C文件的main函数

-

用户堆栈配置

实则是对一大堆数据结构进行预处理然后执行main。我明白了。:happy:

-

-

-

-

三种下载方式

-

ISP(In System Programing,在系统编程)

-

ISP是一种无需将芯片从电路板上取下,就能对其内部程序进行烧录、更新的技术。

MCU 要能进行 ISP 操作,得处于能执行程序的状态,不仅要上电,还得有晶振。而且得预先把 ISP 相关的代码烧录到 LDROM(这里可理解为一块特定的存储区域)里。

烧录的范围只限于 APROM(应用程序存储区)、DataFlash(数据闪存,用于存储数据)或者 CONFIG(配置信息存储区)。即便芯片处于 LOCK(锁定,防止程序被随意篡改等)状态,也能更新这些区块里的内容。因为烧录动作由 ISP - code 控制,所以给系统设计者很大的灵活度。

-

STM32中的ISP下载方式:

-

把 BOOT0 设置为 1,BOOT1 设置为 0,然后按下复位键。

这样设置后,STM32 就会从 Flash 的系统存储器启动。系统存储器里存着 BootLoader 程序,这是进行 ISP 下载的关键。

-

在系统存储器里的 BootLoader 程序的帮助下,把工程生成的.HEX 文件,通过串口助手(比如 FlyMcu )下载到 STM32 的 Flash 主存储器中。

-

把 BOOT0 设置为 0,BOOT1 设置为任意值(用 X 表示),然后按下复位键。此时 STM32 就会从 Flash 的主存储器启动,这样下载好的应用程序就能正常运行了。

-

-

-

ICP(In Circuit Programing,在电路编程)

-

MCU 只要处于上电状态,不需要预先在 MCU 内部烧录任何代码。烧录范围能覆盖整个 MCU 芯片。当芯片处于 LOCK(锁定)状态时,没办法直接更新某一个区块。只能先执行 erase - ALL(全擦除)操作,之后才能更新某一区块,然后再逐个把其他区块烧录回去。

-

STM32中的ICP下载方式:

启动方式是从 Flash 的主存储器启动(设置 BOOT0 = 0,BOOT1 为任意值,用 X 表示)。

一般是通过 JTAG、SWD来进行程序下载。

-

-

IAP(In Applicating Programing,在应用编程)

-

MCU 在运行的状态下,利用 ISP 的机制,不借助外接工具的帮助,就可以去更新 APROM(应用程序存储区)、DataFlash(数据闪存)或者 CONFIG(配置信息存储区)。

-

IAP相关说明:

ICP 是直接把程序下载到 Flash 中

ISP 则是通过 BootLoader 程序下载到 Flash 中。

虽然 ISP 里的 BootLoader 程序用户通常不可以直接更改,但用户是可以自己定义类似功能的程序的。

接口可以通过有线和无线的方式进行下载。

-

-

-

三种硬件电路

-

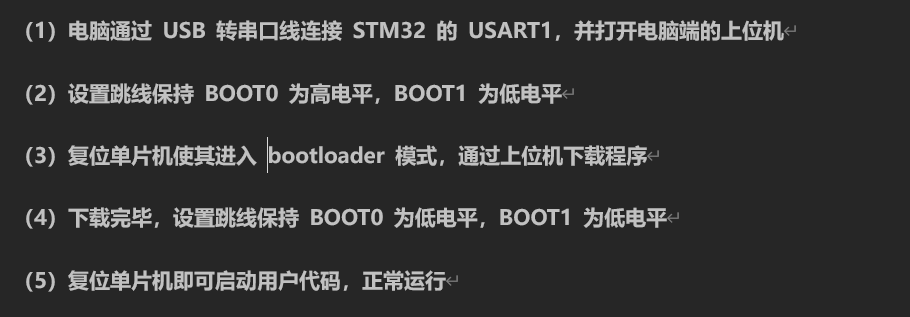

串口ISP电路

在使用串口下载ISP的时候,将BOOT0上拉,接到3.3V,将BOOT1接GND。

-

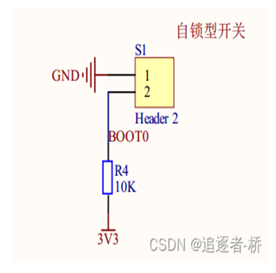

JTAG下载调试电路

-

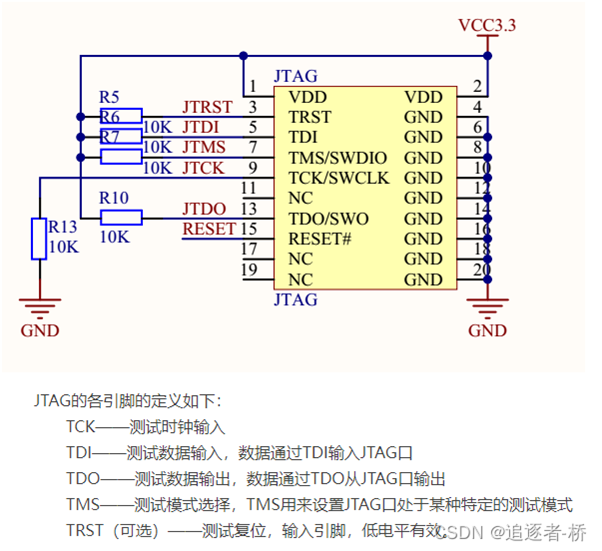

SWD下载调试电路。

SWD在高速模式下要比JTAG模式更加可用。

我们在使用SWD模式时,对BOOT0和BOOT1需要做如下处理,

将BOOT0悬空(或接高电平),将BOOT1经过一个10K的下拉电阻拉低。

-

-

电源电路设计

-

电源介绍:

-

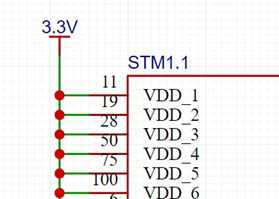

电压:1.8V~3.6V

-

类型:数字电源VDD、模拟电源VDDA、备份电源VBAT。

-

调压器:输出电压约为1.2V

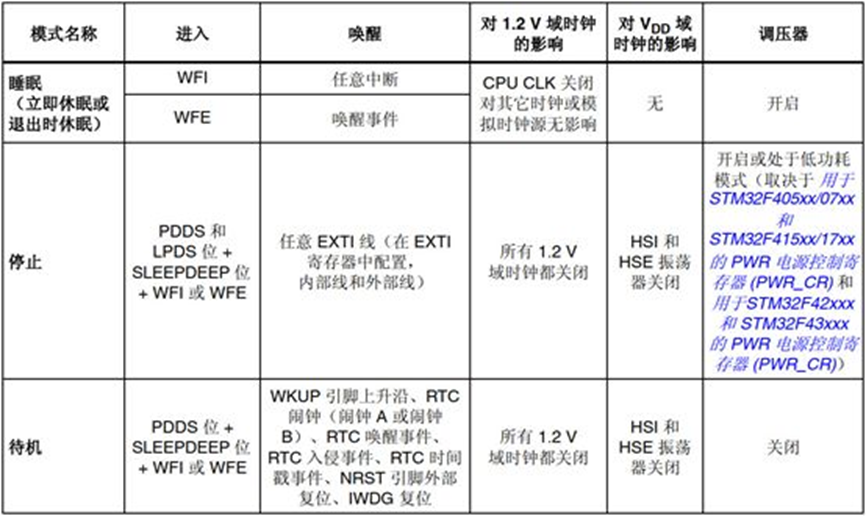

运行模式:调压器为 1.2 V 域(内核、存储器和数字外设)提供全功率。

停止模式:调压器为 1.2 V 域提供低功率,保留寄存器和内部 SRAM 中的内容。

待机模式:调压器掉电。除待机电路和备份域外,寄存器和 SRAM 的内容都将丢失。

-

-

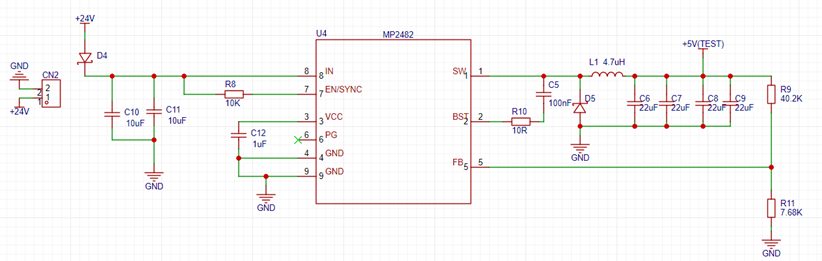

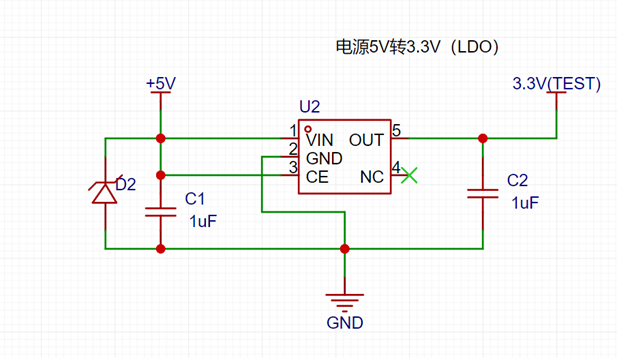

供电电路设计

车上的供电电压为24V,单片机的电压要求为3.3V,我们对24V的电压进行输入降压。

经过24-5-3.3的降压给到单片机。

-