今天收到了朋友送我的一本书(真的万分感谢,在国外买本书太不容易了,更何况朋友是直接从国内买了送给我),B站UP主JT编写的《高速PCB设计经验规则应用实践》,便趁热打铁上手看了起来。在第一章,1.5.3小节,了解经验规则的原理这一段中,JT提到了一条关于“PCB走线不能走直角或锐角”的规则,并且对于这一规则给出了自己的分析与见解。分析这一规则的文中提到了有一篇IEEE论文证明直角没有增加板子的EMI,也即辐射,不过JT并没有提到这一论文具体的内容。于是我写下这篇随笔,分享一下JT对于“PCB走线不能走直角或锐角”的看法,以及JT提到的这篇IEEE论文。

JT的看法:

对于“PCB走线不能走直角或锐角”的规则,业内常见的说法有三条:

1阻抗不连续,会引起信号反射,直角处还通常分布有寄生电容,影响信号的上升下降沿;

2直角的尖角会增加EMI;

3PCB制造过程中,直角的地方会聚集腐蚀液造成线路断线。

对于业内的这三点看法,JT并不完全认同。

首先,假设一条特征阻抗50欧姆,宽度4mil的走线,一个直角带来的分布电容量约为0.01pF,可以估算出由此引起的信号上升时间变化量约为0.5ps。其次根据公式计算出来的反射系数最大约为0.1,符合10Ghz一内信号对于发射系数控制的要求。JT的结论是直角或者锐角走线可能对阻抗的变化其实很微小,对信号影响不大,除非是30GHz以上的超高频PCB,应当以圆弧拐弯。不然,在一般设计里,无论45度拐弯还是直角拐弯,甚至任意教务拐弯都没有什么区别。

这里我说明一下估算直角走线的寄生电容可以将其视作一个局部铜面积增加区域,从而近似为一个平板电容结构。寄生电容估算公式如下:

其中:

代表PCB材料的相对介电常数,一般FR4板材是4.0

代表PCB材料的相对介电常数,一般FR4板材是4.0

为8.854×10-12 F/m 真空介电常数

为8.854×10-12 F/m 真空介电常数

A是直角区域的铜面积,单位平方米

d是信号层与参考层之间的距离,单位米

假设走线宽度为4mil,即0.1016mm,那么直角区域面积A近似为走线宽度的平方,为1.03×10-8 平方米,层间距为1.9mm(以双层板1盎司铜皮2mm板厚为例,信号层到参考层的间距就是板厚减去1mm),那么计算得到的寄生电容只有0.192 fF是远远小于经验公式计算出来的0.01pf的,因而对信号时延的影响原始远远小于0.5ps,根据:

![]()

R为特征阻抗50欧姆

C为寄生电容

可以算出时延只有9.6fs

这里提一下,根据电路知识这个时间常数1其实并非是准确的电容只充电到63.2%。按照电容充电80%计算出来的时间常数应该是1.61,所以更保守的估计时延影响应该是15.46fs,不过,不管是寄生电容经验估算公式还是按照平板电容估算公式,走线直角对于信号时延/上升沿的影响可以说微乎其微。

然后从阻抗角度来看,直角走线时的阻抗变化会导致信号反射现象,不过这个反射对于10Ghz以下的信号来说一定是致命的吗?我们可以从回波损耗Return Loss, RL 或者反射系数 来量化这个问题:

来量化这个问题:

其中:

Zs和Zo分别为阻抗不连续处的两侧特征阻抗。一般直角走线造成的阻抗变化为7%-20%,所以可以计算得到反射系数最大为0.1。

这里JT并没有提到反射系数0.1即10%对于高速信号来说是什么质量,所以要提到上面说的回波损耗RL了:

回波损耗和反射系数是对数关系:![]() ,所以10%的反射系数对应的RL是20dB

,所以10%的反射系数对应的RL是20dB

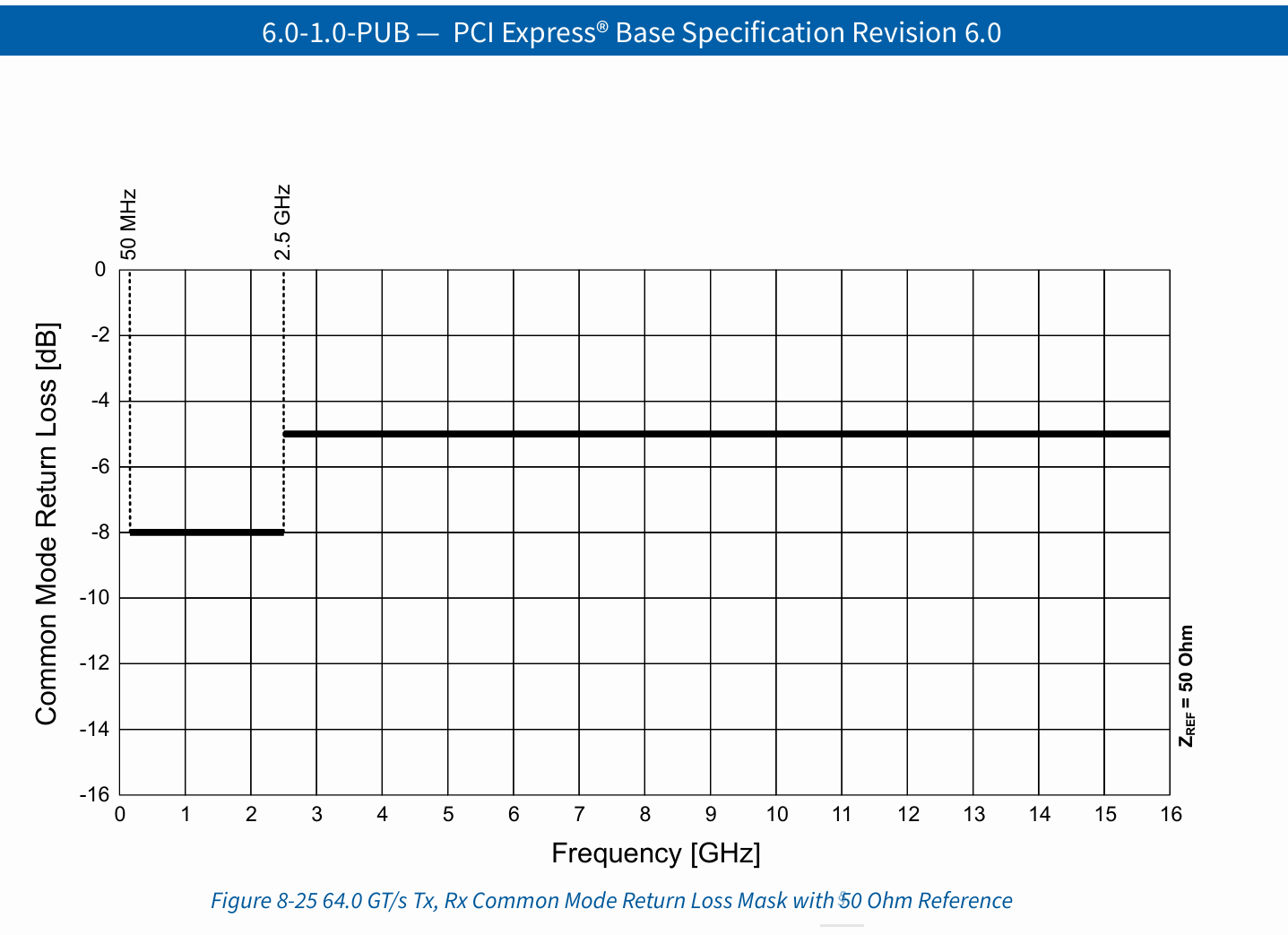

从PCIE 6.0的SPEC中可以看到对于RL的一些要求:

这里要注意图中的RL是负值,实际上我们应该取绝对值去看。因为我们使用仪器(网分)是进行S参数测量(S-parameters S参数通过指定反射信号的幅度和相位,描述射频信号如何响应设备端口的值。该名称来源于“散射 Scattering parameter”的S),由于 S参数测量的性质,S11 (dB) 通常为负值。对于无源器件,S11 中捕获的反射波与入射波的比率不应超过 1。当该比率以分贝表示时,仪器的输出结果始终为负值。 S11 的最高值为 0 dB,对应反射系数为 1。所以图中的RL实际上是S11,是“损耗”这一词的相对含义。当然直接简单粗暴取绝对值就行了,不影响理解。从这里可以看出,50MHz-2.5GHz频率内,PCIE6.0 SPEC推荐的RL需要大于8dB,2.5GHz-30GHz频率内,PCIE6.0 SPEC推荐的RL需要大于5dB,换算成反射系数就是39.8%和56%相比之下10%的反射比是相当优秀的水平。这里我也咨询了通信行业的前同事,他给我的回复也是实际情况下3比1(25%)或者2比1(33%),射频方面的性能就能达到理想指标了。捎带提一下:USB4 Gen3的RL限制是>10dB @15GHz,可以算一下对应的反射系数是多少。

所以直角走线带来的阻抗不连续问题,在一般电路,或者说30GHz频率一下的电路而言,也并非是什么原则性问题。

其次,直角走线会影响EMI性能,对于尖端放电而言,至少需要上千甚至上万伏电压才能击穿空气或电路板绝缘层,一般而言,PCB上走的信号远远达不到这个标准。

最后,在上世纪90年代PCB制版工艺落后,直角走线或者锐角走线,的确会在一定程度上造成酸液堆积导致线路腐蚀开路的问题。但是经过几十年的技术迭代,现在的PCB制版技术已经十分完备,因此这个说法也并不成立。

综上所述,“PCB走线不能走直角或锐角”的规则,从一定程度上来看,并非拥有充足的、令人信服的理由让人一定去遵守。在一般电路板,或者10GHz以下的电路板中,走线的角度,无论是直角还是锐角,对于信号质量产生的影响都是微乎其微的。JT也举了一个例子:HP的3456A六位半台表就是经历了大量市场检验,并且PCB上布满了直角走线的经典例子。我也十分赞同JT的观点:并非是提倡走直角,只是想提醒大家,如果你看到有直角或者锐角走线的电路板,不要急于批评别人。我们不能光看经验规则的表面,更应该了解经验规则背后的原理,才能明白规则的本质,才不会望文生义或者人云亦云。

文章的末尾分享一下

Mark I Montrose先生的看法:

作为EMC专家,马克在IEEE上发表了一篇标题为《Right Angle Corners on Printed Circuit Board Traces Not a Source of EMI》的论文,目的是通过实测数据来反驳长期以来关于 PCB 走线中直角转弯会导致电磁干扰(EMI)和信号完整性问题的“经验法则”。可以看出马克对于所谓“PCB走线不能走直角或锐角”的规则,其中原因之一——直角或锐角走线会导致EMI问题表示反对。

在这篇论文中马克设计了两块 PCB 进行测试:

PCB 1

- 双面板,厚度 0.062 英寸

- 三种走线宽度:5 mil、10 mil、20 mil

- 三种转角类型:90°、45°、圆角

- 每种配置有 6 个转角,总长度 18 英寸

- 参考地路径可切换:无地、底层地平面、近距离地填充(guard band)

PCB 2

- 四层板,走线宽度 7 mil,长度 8 英寸

- 精确控制阻抗为 50 欧姆

- 用于观察单个转角的影响

时域分析(Time Domain Analysis)

主要发现:

- 所有转角类型(90°、45°、圆角)在时域中引起的阻抗不连续性非常小(约 30 ps 的“glitch”)。

- 这些阻抗变化不足以影响信号完整性,除非信号上升时间小于 15 ps(即频率高于 33 GHz)。

- 多个转角若距离很近,会被视为一个整体的阻抗不连续性,影响进一步减小。

- 计算得出的额外电容值(如 0.014 pF)对 10 GHz 以下的信号影响极小

频域分析(Frequency Domain Analysis)

测试方法:

- 注入 40 MHz 谐波信号,测量 30 MHz 到 1 GHz 的辐射。

- 比较不同转角配置下的辐射强度。

主要发现:

- 没有参考地路径时,辐射显著增加。

- 有参考地路径(无论是底层地平面还是 guard band)时,辐射降低 20–30 dB。

- 90°、45°、圆角之间的辐射差异非常小,最多在某些频率点有 2–5 dB 的差异。

- 辐射主要在高于 750 MHz 的频率才开始显著,但幅度仍然很小。

时域方面:

- 90° 转角不会引起可测量的信号反射或显著的阻抗不连续性。

- 除非信号频率非常高(>30 GHz),否则不需要担心转角对信号完整性的影响。

频域方面:

- 90° 转角不会显著增加 EMI。

- 辐射主要由其他因素引起,如器件封装、连接器、过孔、共模电流等。

- 角落的辐射在高频段才可能出现,但幅度很小,几乎无法测量。

马克建议工程师在设计PCB的时候:不要过度担心PCB中的直角走线,尤其是在低频低速电路中;工程师在设计PCB的时候,设计重心应该放在参考地的回流路径、器件布局、过孔控制和共模电流控制等更加关键的因素上。