上一篇讲了rf data converter这个ip核整体的时钟结构 以及rfdc的运行机制,在我们实际应用的过程中,还需要在PS端通过配置寄存器的方式启动时钟,而通过TICS PRO这个工具,我们可以直接更改参数的形式就完成对于时钟配置

下面结合TICS PRO这个软件讲解一下时钟应该如何配置

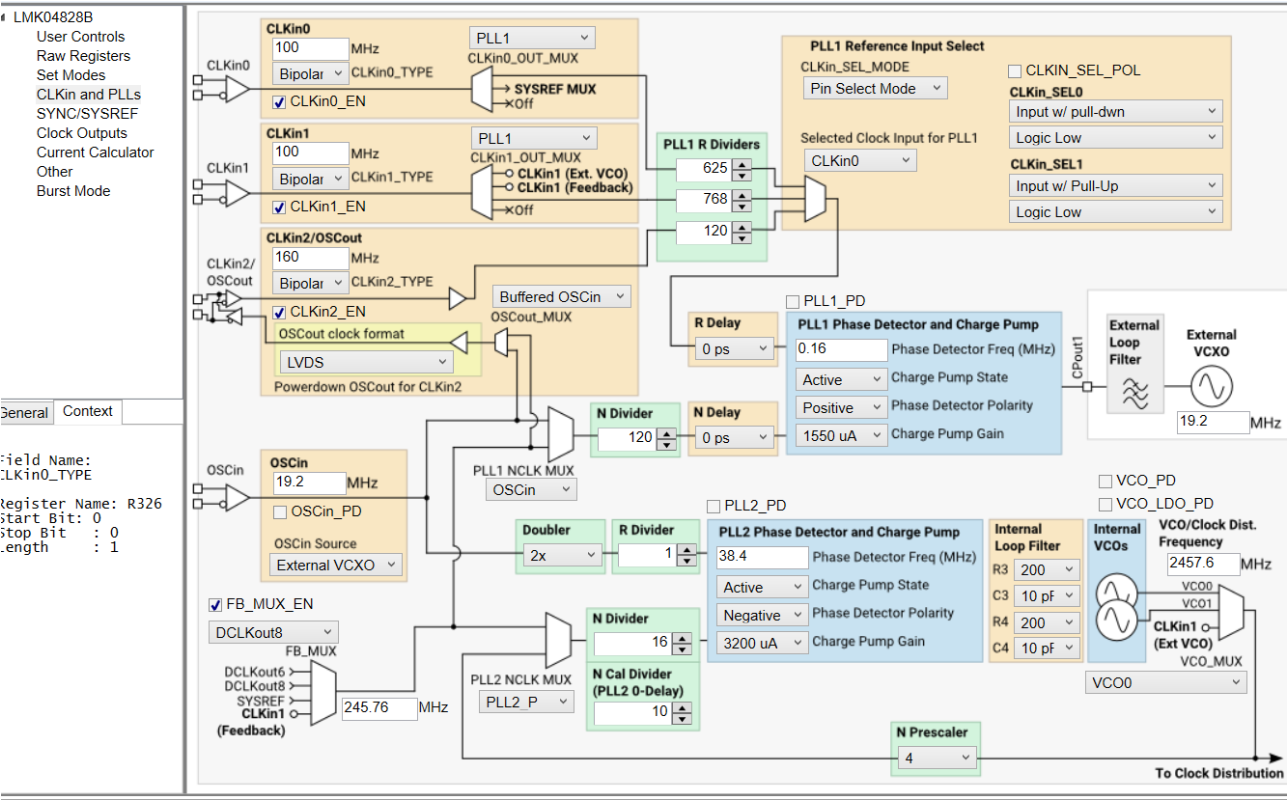

打开软件后选择LMK04828这款芯片,然后工具栏里有一条default configuration,里面有一些默认配置可以直接用

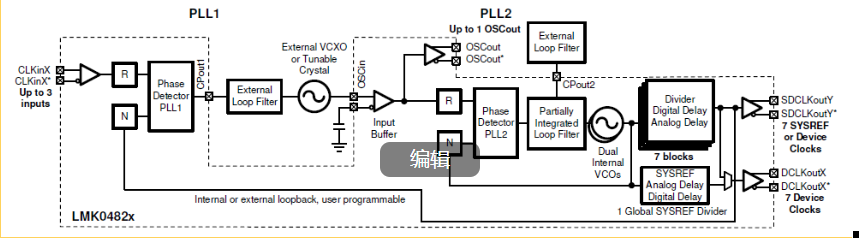

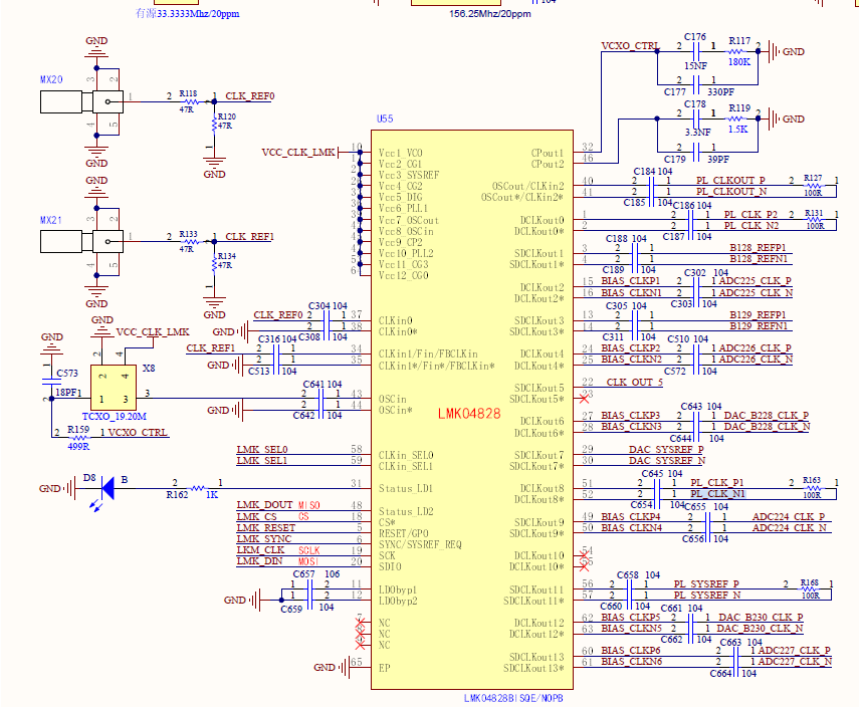

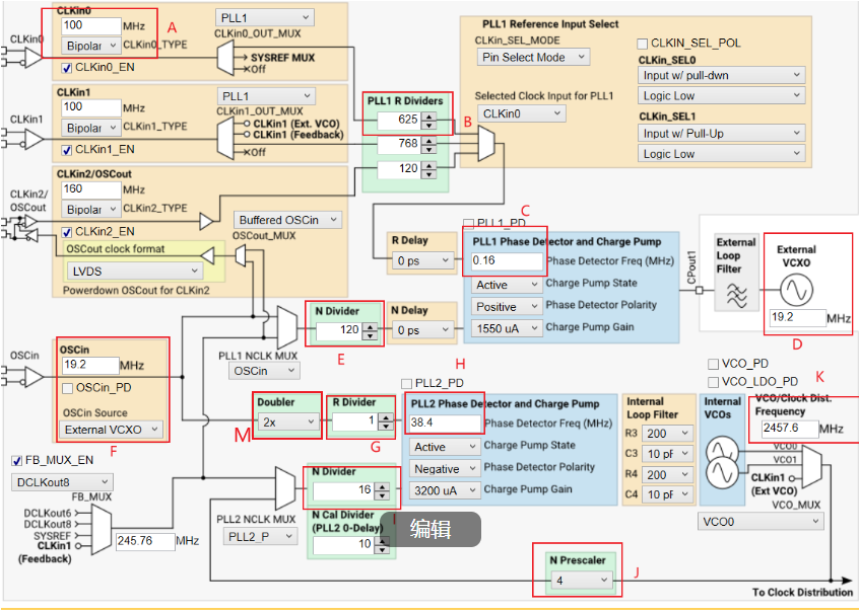

结合着软件界面和手册给的图,我们可以看出来LMK04828有两个层级输入,一个是OSNin(外部晶振的输入),用来作为内部VCO/PLL2的振荡参考源,还有一层是CLKin012这样的外部参考时钟输入,是PLL1的参考输入端口,可以选择多个外部参考时钟源(比如板卡上的33.333,100,156.25MHz),我这里选的是100MHz,用来与OSCin/VCOX比较相位,进行锁相核频率同步。

我们可以把LMK04828看成两层的PLL,第一层由外部参考时钟(来自 CLKin0 / CLKin1)输给PLL1(PLL1 用外部参考锁 VCXO,相当于“锁外部系统”),然后 控制电压调整 VCXO (接到 OSCin),然后接到PLL2输出多个低抖动时钟DCLK_OUT

PLL1

我们再结合一下手册里的标准图例看一下,这张图我们能很清楚的看到PLL1和PLL2的结构

PLL1输入参考时钟包括管脚CLKin0,CLKin1以及CLKin2.可以选择任何时钟输入,输入之后把外部参考(CLKin0/1/2)的低频稳相信息给到内部振荡源(VCXO / OSCin),用于与外部系统同步或作为参考切换,主要传递低频相位/频率信息(长时稳定性),通常不希望把外部参考的高频抖动传给 VCXO,通常设置较窄或中等带宽,所以我们看到的external VCXO的值通常会很小,避免把参考信号的高频噪声带入

这里说一下VCXO和最后输出VCO0/1的区别

VCXO(Voltage Controlled Crystal Oscillator)是一个电压控制晶振,它输出一个相对稳定、低相位噪声的中频时钟,典型值有19.2MHz,100MHz等,石英谐振器频率非常稳定,可以通过电压微调,由PLL1的相位比较器输出电压驱动实现相位锁定,作用是使锁相外部参考信号

VCO(Voltage Controlled Oscillator)是高频的电压控制振荡器,LMK04828这款芯片的VCO0 在2370到2630MHZ,VCO1在2930到3080MHZ,他是以VCXO作为输入来源,通过倍频产生各种高速的输出频率

PLL2

PLL2的主要功能就是接收低频锁相后的信号之后生成高频低抖动的输出时钟,并完成频率的合成与分配,在保留与外部信号同步的同时抑制外部参考的高频噪声,PLL2往往支持更高倍频与更小的分频步长,在通过完整的锁相过程(鉴相-环路滤波-反馈分频之后)控制VCO产生与参考信号通向的高频振荡,然后再通过分频(output divider)后产生DCLK/SDCLK等信号,从而给ADC DAC Fabric等时钟提供精确的高速时钟,同时sysref信号也是由PLL2分频生成的

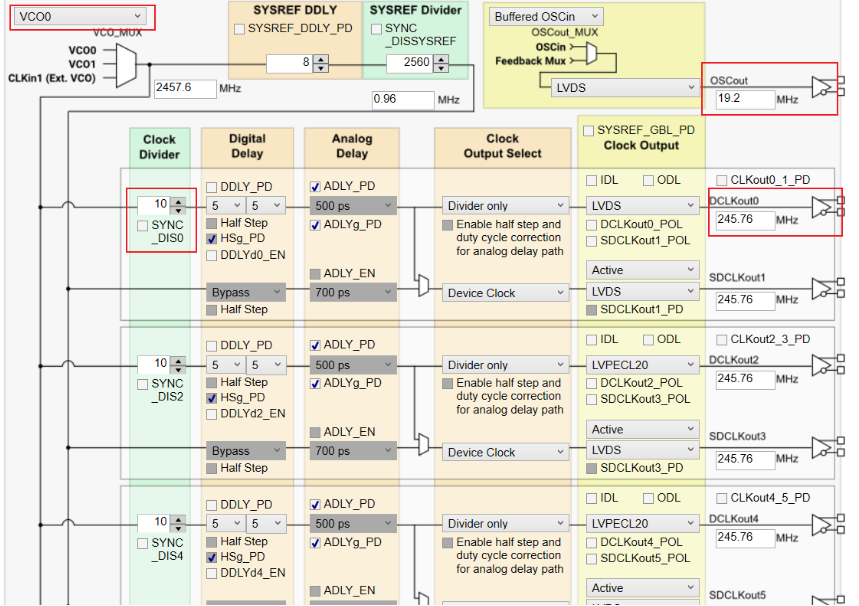

看一下原理图上时钟的引脚我们可知,右边的out都是由PLL2产生,可以用来提供给PL_CLK ADC_CLK,DAC_CLK,PL_SYSREF等引脚

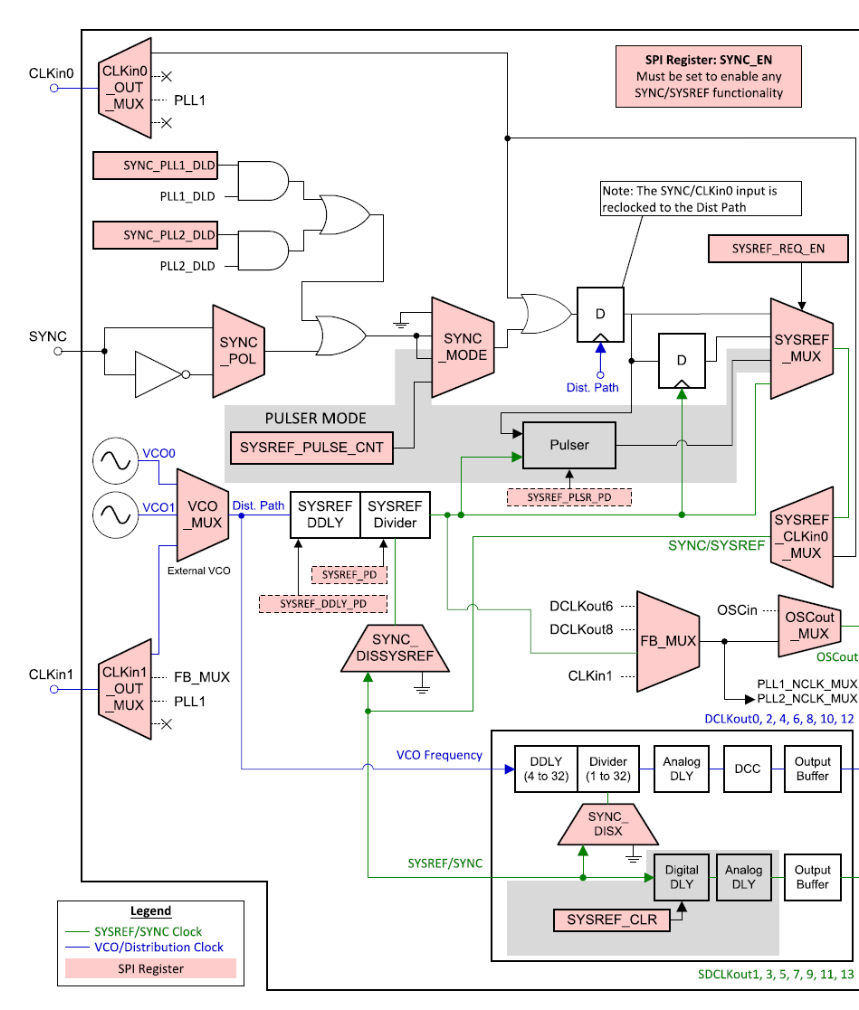

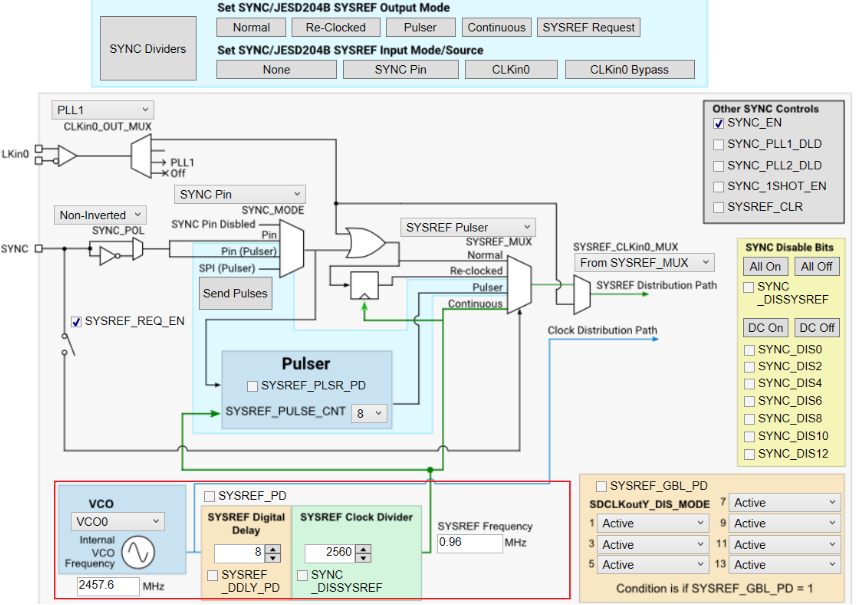

作为时钟同步体系里面重要的信号,我会在下一篇讲一下多片同步的概念,但是在这里先介绍一下这两个核心同步模块

SYNC核(Synchronization Core)负责内部时钟相位和输出相位的同步

SYSREF信号负责JESD204的链路同步

SYNC接收外部同步请求信号(SYNC pin / SPI 命令触发),复位所有输出分频器,使所有输出时钟在同一参考边沿重新开始计数,重新输出 SYSREF 脉冲

SYSREF是多设备(FPGA adc dac)之间的共同时钟标记,告诉这些设备在某个时刻,所有的帧边界需要对齐,其是由PLL2的VCO时钟经过内部逻辑分频产生,可以配置为单次脉冲(One-shot),周期性脉冲(periodic)和禁止输出(powerdown)

其要求

- 必须与DCLK相位对齐,否则JESD204接收端无法检测正确边界

- 边沿应稳定,这点只要锁定PLL2后输出就可以

- 时序应该与DCLK成整数倍关系,因为是分频得到这个,要确保帧边界稳定

- 建议通过SYNC触发产生,避免时序漂移或者毛刺

可以理解为SYNC是控制命令,SYSREF是控制结果

接下来看一下如何配置

配置

在配置的时候这些框里的数字都互相影响相关,大家在配置的时候可以多做尝试,最主要的两个地方是D和K,注意一下VCO0 在2370到2630MHZ,VCO1在2930到3080MHZ,我这里使用的是VCO0输出,设置了2457.6mhz方便后续分频产生245.76mhz

在这里C = A/B = 0.16;

D = CE = 0.16*120=19.2;

F = D = 19.2;

H = M*F/G= 19.2*2/1=38.4;

K = HIJ = 2457.6;

然后在这边SYNC和SYSREF信号是共享同一条时钟路径,也就是说同一时间,只能用其中一个的功能,要么使用SYNC实现同步功能,要么是输出SYSREF

在这里要注意en信号必须勾选使能,且低电平持续时间必须大于一个DCLK周期,过段的sync脉冲可能导致识别不了复位

随后进入output配置页,在这里VCO0和上面的参数是由前两页你的配置决定的,更改不了,通过更改下面clk divider来改变out的输出,然后对着原理图上每个out分别对应的是哪个引脚,再和你在ip核配置的时候选择的时钟频率对应上就可以了

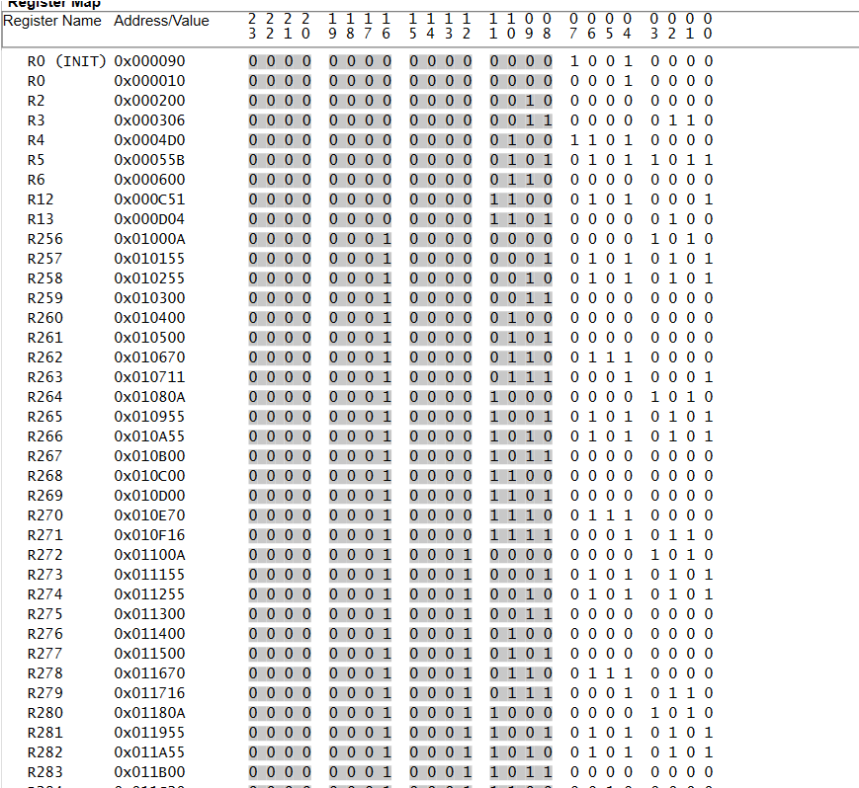

在这里我们把上方options-autoupdate打开,这样每次更改之后寄存器的值就会自动更新,在这里就可以直观的看到24位2进制结果的寄存器

然后我们点击上方File - export hex register values,把这个16进制文件导出来,导出来之后我们使用notepad编辑器给他们列对齐之后加上逗号,就可以导入Vitis进行使用了