一直想完整的完成从FPGA到RTOS再到基础APP完成整个流程的理解,于是,尝试在开源的小麻雀操作系统上移植最简单的UCos-III移植,但由于不懂Verilog,所以磕磕碰碰,以下是其记录:

准备工作

由于使用的是一块小小的 Tang Nano 20K 开发板,其芯片为高云的 GW2AR-18C,且 SparrowRV 的作者已经提供了该开发板的移植实例工程,只需要在上面改一改就可以用了。

- 搭建高云的开发环境,从官网下载最新版即可;

- 在Gitee上拉取 SparrowRV ;

- 搭建Bsp的开发环境,这里使用的是Windows上的 MounRiver Studio,这个商业版或社区版都行;

- 拉取UCos-III的源码,去UCos-III GitHub这里,一般只需要拉uC-OS3、uC-CPU、uC-LIB这三个即可;

移植准备

- 首先,得保证FPGA工程可以综合的过,由于高云教育版软件的更新,

fpga/gowin_tang_nano_20k目录下以前的工程直接综合会报错,提示FPIOA引脚电压错误,将其改为3.3V,即LVCMOS33; - 此时可以发现很多FPIOA依旧没有连接到物理引脚上,由于本次只用到了Uart0的Tx口,更具原理图可以得到实际Uart0的Tx引脚是69,将FPIOA的Location改为69,并将Pull Mode改为None;

- 此时综合将不再报错;

- 打开

bsp/bsp_app里的MounRiver Studio工程,最新版本是基于VsCode开发的,不是以前的Eclipse开发的; - 直接编译工程,编译通过即可确保拉下来的是没有问题的;

- 将拉取下来的三个文件夹放到工程根目录下开发环境将会自动添加这些文件夹到项目内;

- 删除工程内除RISCV架构相关的其他架构的文件(注意不要把Cfg文件夹删了);

开始移植

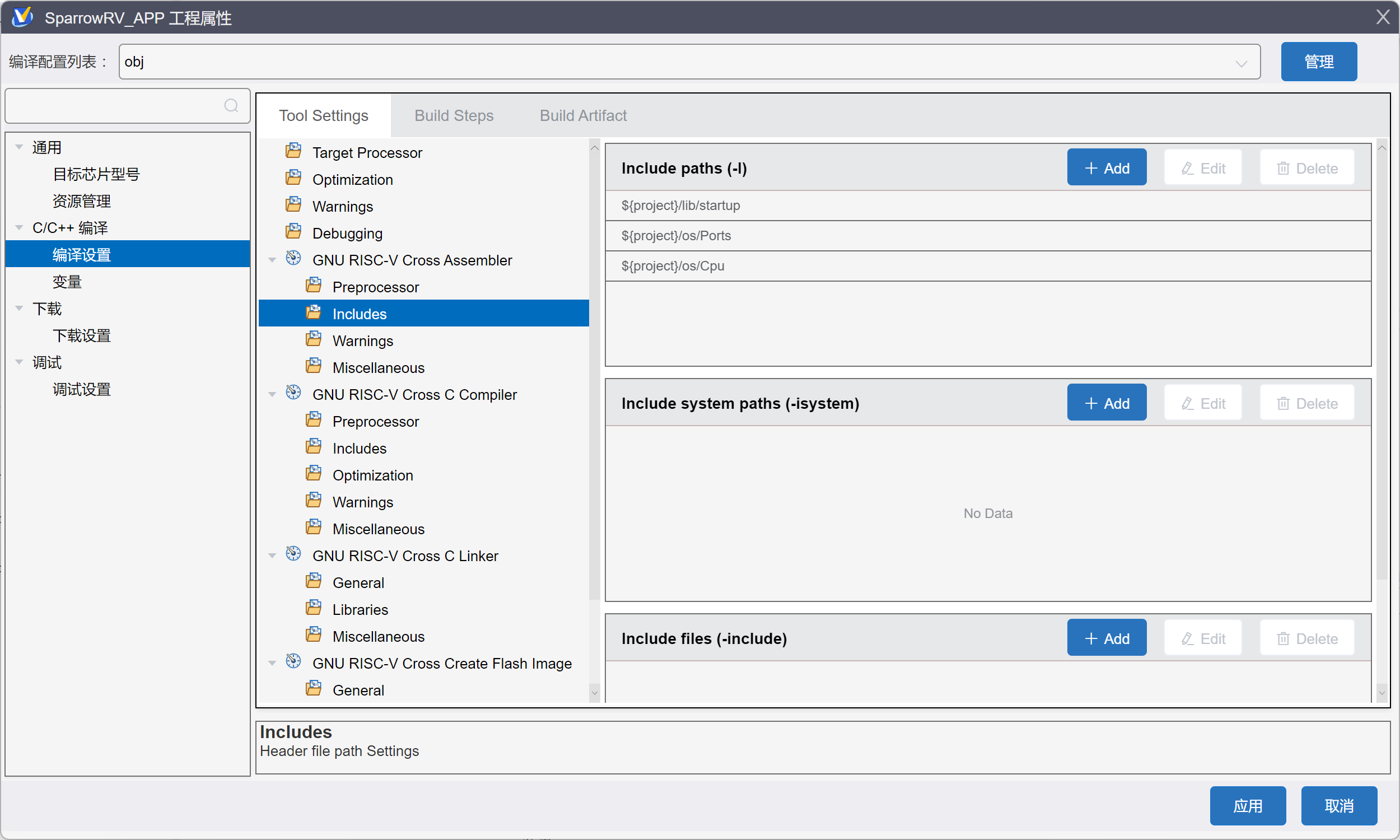

- 配置工程,在设置工程属性里添加头文件目录和汇编文件目录并关闭优化:

- 修改Ports文件夹下的相关文件,这里是关于移植的东西:

os_cpu_a.S

这里关于总中断的地方不用改,因为其CSR寄存器遵循了标准。但是关于软中断切换和主动触发的地方要改:

点击查看代码

.equ RISCV_CSR_MSIP, 0x345 # 添加自定义CSR软中断寄存器地址(写1触发软中断)#-------------------------------------------------------------------------------------------------OSCtxSw:

OSIntCtxSw:

# MIE_MSIE -- 启用软件中断位li t0, RISCV_MIE_MSIEcsrrs zero, mie, t0# 这将触发一个同步软件中断 MSIP = 0x01;csrrsi x0, RISCV_CSR_MSIP, 1ret#-------------------------------------------------------------------------------------------------Software_IRQHandler:

# 禁用全局中断并防止上下文切换期间的中断li t0, RISCV_MSTATUS_MIEcsrrc zero, mstatus, t0# 清除 hart0 的软件中断,MSIP = 0x01;csrrsi x0, RISCV_CSR_MSIP, 0...

安装中断

想要UCos-III跑起来,主要需要安装两个中断函数,它们都在Ports内,分别是 Software_IRQHandler 和 SysTick_Handler。

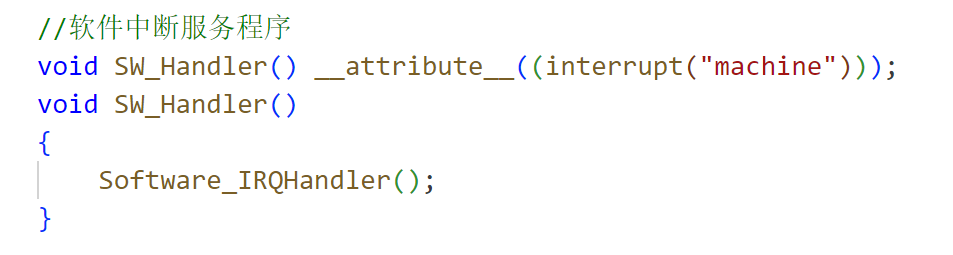

由于 SysTick_Handler 和示例Bsp里的函数重名了,这里直接注释掉 trap_handle.c 里的定义就好,注意不要注释掉声明,因为它声明使用了 __attribute__((interrupt("machine"))) 。

然后在 trap_handle.c 里直接调用UCos的Software_IRQHandler。

调用系统

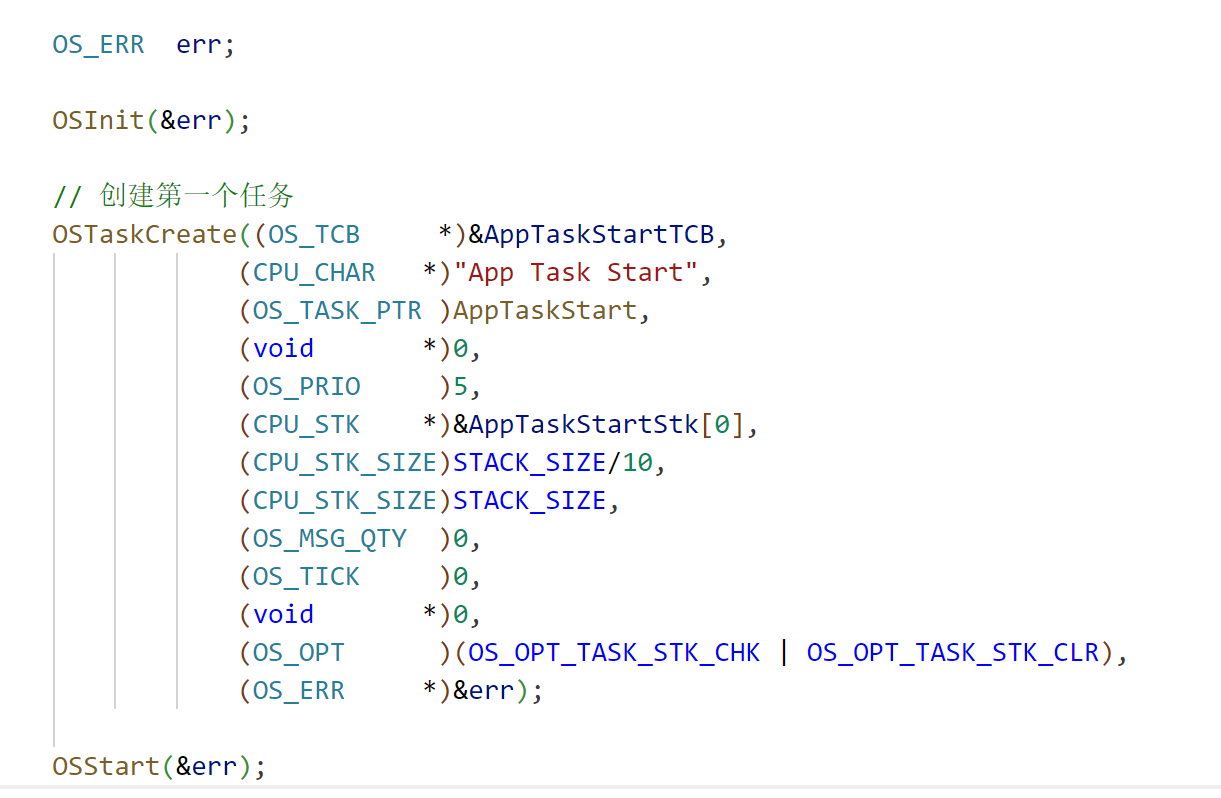

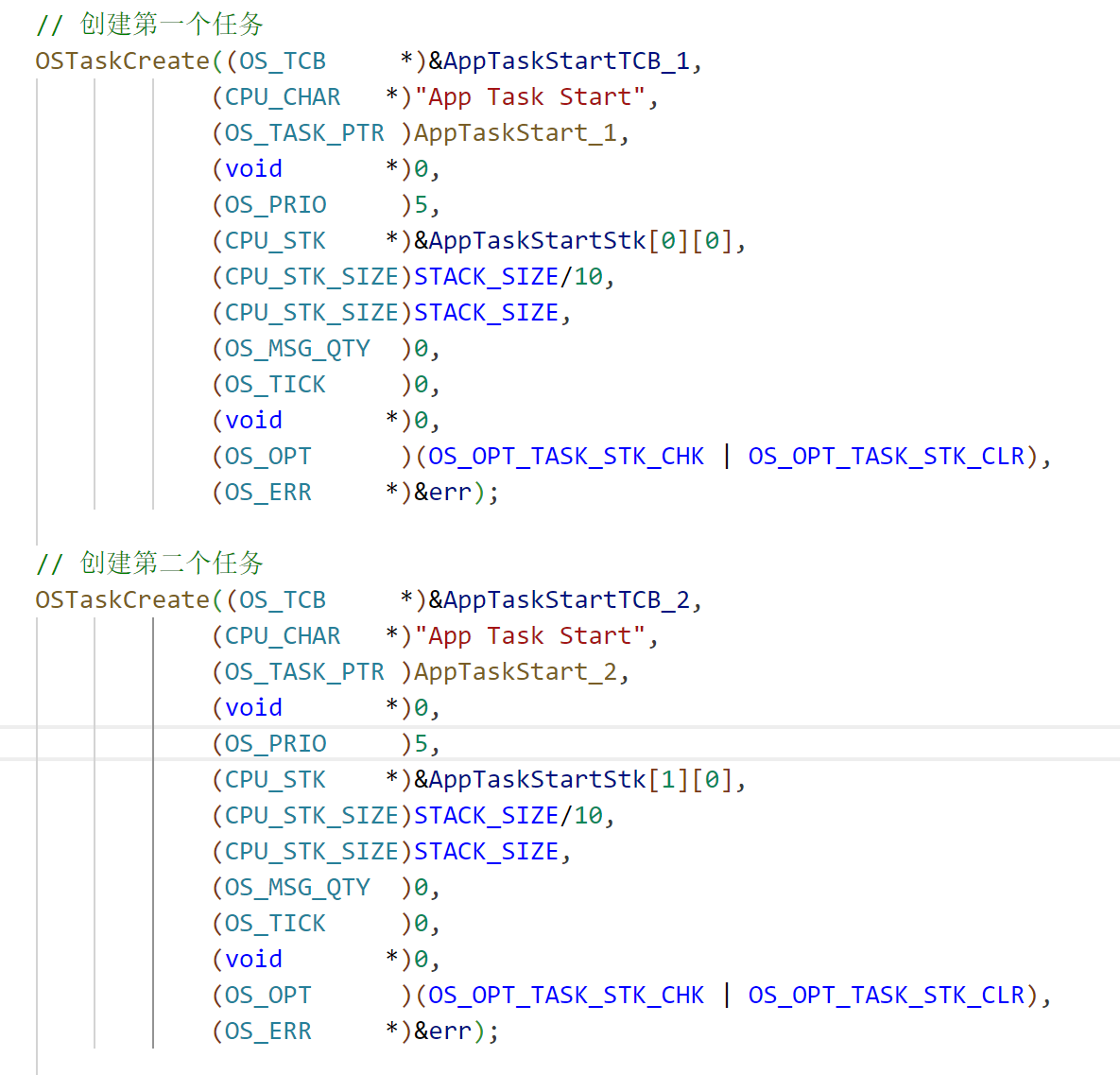

在 main 里调用 OSInit 、 OSStart ,顺带创建个任务。

到这里移植就基本结束了,接下来就是写两个简单的任务。

基础应用

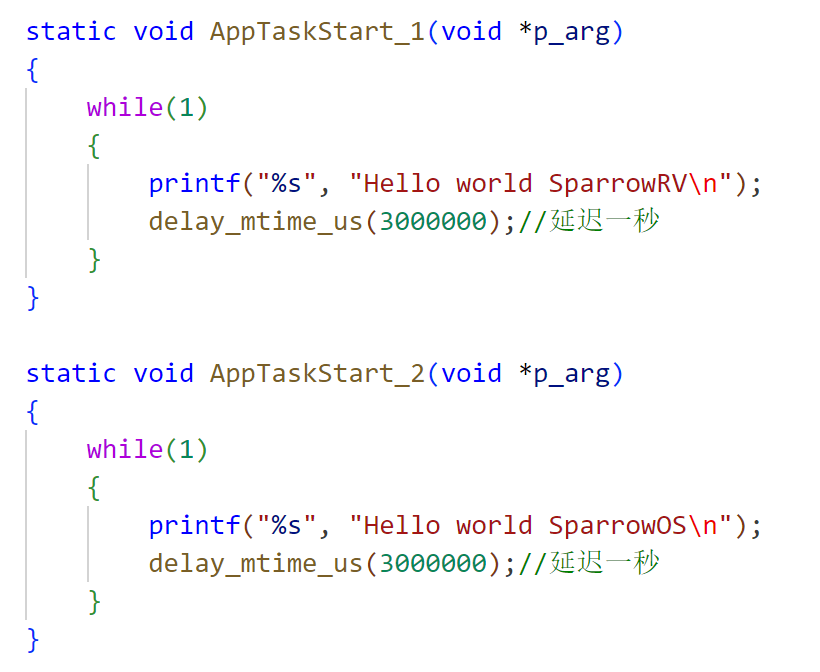

编写两个任务:

完成。