西电PCB设计指南第4章学习笔记

四、电源路径分析

-

电源路径的基本原理

-

回路路径与感抗

感抗与路径有关,信号线看似很短很直,但是引入了较大的环路感抗。多路信号线的环路之间的互感,造成相互干扰

所以,我们不能但按照最短路来布线(导线越长电阻越大),要考虑产生的感抗大小。

-

降低回路阻抗的方法(重要)

-

减小面积:减小环流面积,能有效降低感抗分量

-

就近配置:为每一个前向信号配置就近的回流路径,不仅能够减小环路感抗,还能有效降低环路之间的互感

-

信地交替:排线的交替接地布置,信号-地线 顺序交替排列

-

指导性原则: 不要怕信号线长、不要怕曲折,但一定要为之提供一条环路面积小(低环路阻抗)的回流路径

-

一点接地:“一点接地效果好”,只在一个位置走线接地

-

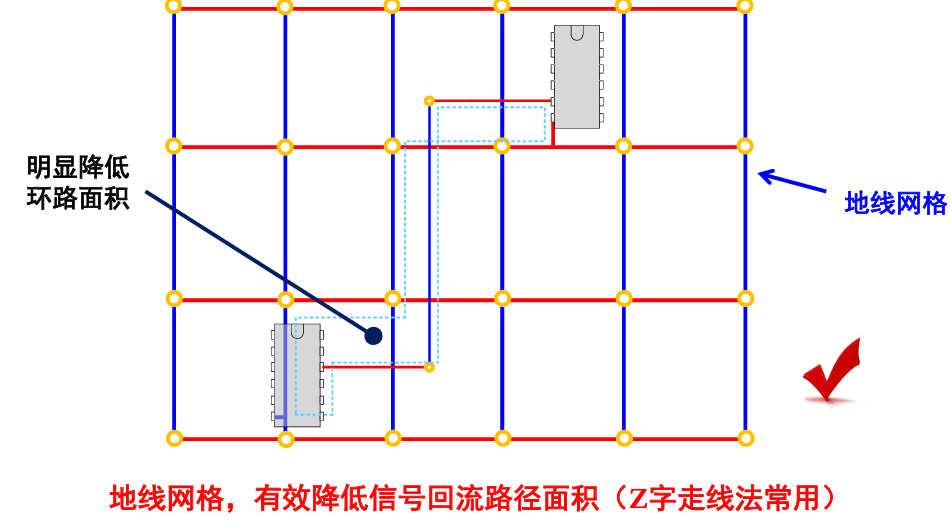

地线网络:

-

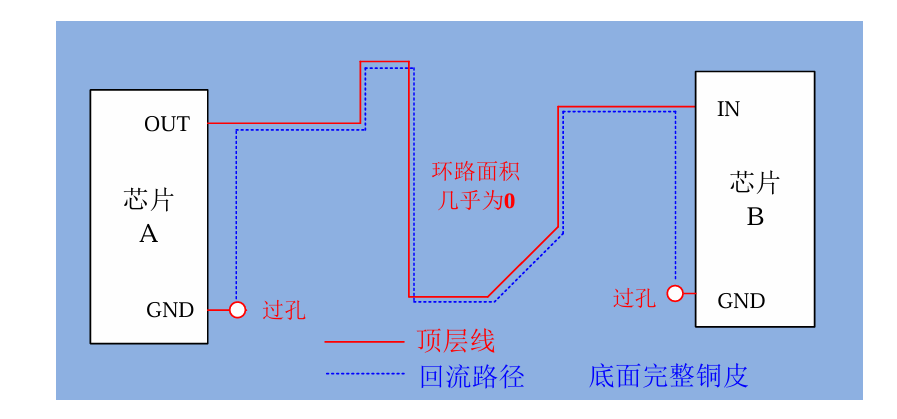

低阻抗平面: 在布线区域保留一个完整的导电平面(低阻抗平面),在其上方任意走线,电流都能自动得找到最小环路回流路径(在信号线正下方)

回流路径位于信号线正下方,大幅降低了相邻导线之间的互感

或者我可以理解为:先连完其他的信号线,然后覆铜之后打缝合孔,再将GND管脚与缝合孔相连?看图应该是这个意思(

-

柔性PCB排线

底面是完整地平面,顶面全是信号线

-

多层板的电源层(高经费消耗)

多层板每个信号层下方都衬有有完整低阻抗平面,

这样信号层任意曲折走线都能保证回路面积很小(即使采用自动布线)

-

-

低阻抗平面的割裂问题

-

短线+过孔搭桥

-

利用另一面的铺铜进行搭桥

-

-

回流路径跨层的处理

-

出现的问题:

多层板的信号切换层时,回流路径也随之跨越低阻抗平面,当内层平面分属不同网络时,回流路径被切断

-

处理方法:

在信号换层过孔附近增加一枚高频电容,用于回流路径的跨层通路

-

-

-

公共路径和公共阻抗

-

公共阻抗

-

概念:

大电流通过某些电路之间的公共路径时,其阻抗引起的压降会叠加在环路中,引起相互干扰

-

消除:

-

混合电路中,将敏感部分和干扰强烈的地线分开,消除了公共路径

-

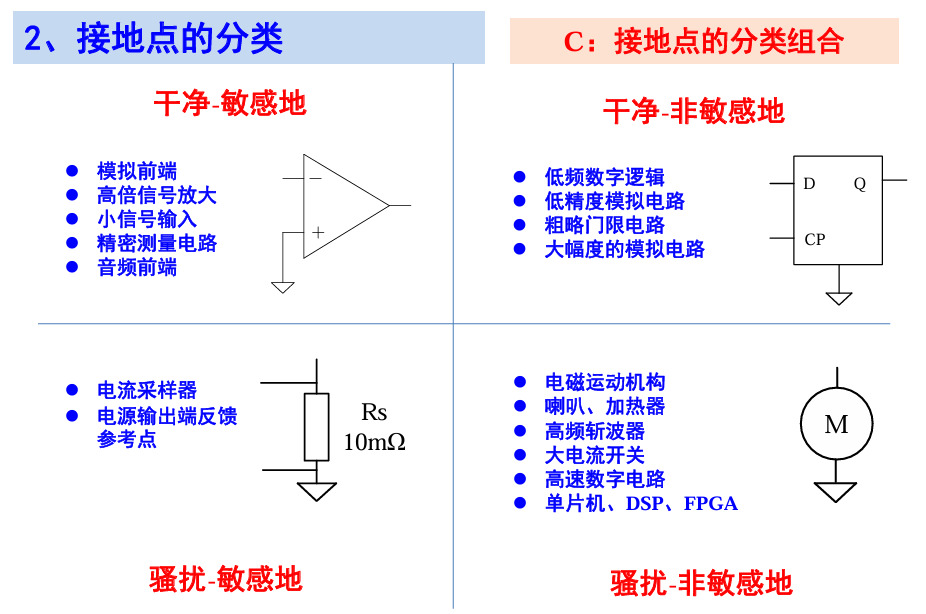

不要用“模拟地”“数字地”的名称(定势误解为模 拟电路和数字电路的地线,实际并不一定)

-

如何判断:

- 敏感地: 地电位轻微偏移也不可容忍

- 非敏感地: 容许地电位较大范围偏移

- 干净地: 电流小、频率低(或直流),接地点电位几乎不变化

- 骚扰地: 有高频/大电流,会引起接地点 附近地电位变化

-

接地点的处理:

-

干净的非敏感地:

接到哪里都行:happy:

-

干净的敏感地:

将这些敏感地尽可能近地连在一起,通过铺铜等手段尽可能降低各接地点之间的阻抗,尽量避免其他电流流经敏感 地所在区域

-

骚扰的非敏感地:

避免骚扰地和敏感地有任何的公共路径,将这些接地点单独连在一起,最后一并连到电源入口处。

-

骚扰的敏感地 :😠

- 若只有一个骚扰敏感点:将此处点作为整个系统的接地点

- 若有多个骚扰敏感点:隔离和差分几乎是唯一手段⭐

-

-

小结:

(1)公共阻抗+大电流流过=相互干扰源

(2)地线分为:敏感、非敏感、骚扰、干净四类组合

(3)保证敏感地点尽可能接近零电位,是最主要目标

(4)避免骚扰地的回流电流经过过敏感地部分,是主要手段

(5)跨接地线割缝的信号线,要避免割缝对回流路径影响

(6)慎重使用磁珠连接

-

-

-

-

电源路径与退耦问题

-

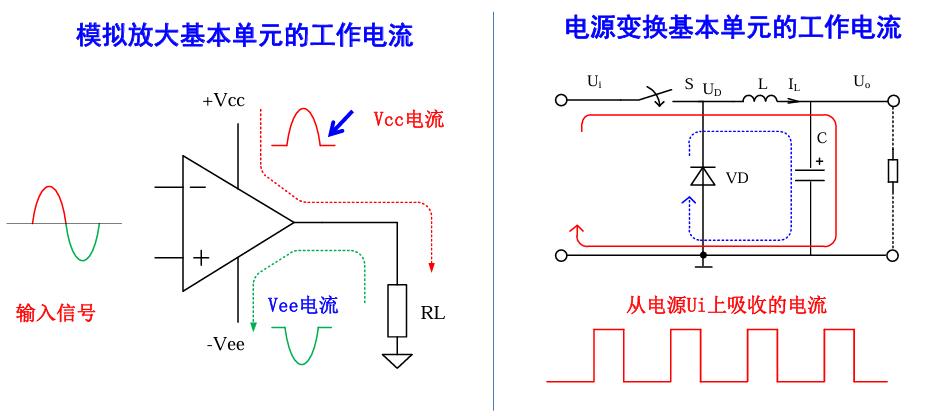

数字芯片的工作电流

数字电路的电流波形都是大电流脉冲尖峰,即使是低功耗芯片;

每一次逻辑翻转,都会伴随电流尖峰产生,测到的是其平均值;

脉冲尖峰电流波形中,包含大量的高频分量!(与工作频率无关)

-

模拟器件的工作电流

模拟器件的工作电流与其信号频率有关,且对于单边电源来说呈脉动状态

功率变换/开关电路,呈现周期性的脉动电流(可能还伴随强烈的高频干扰)

-

电源的环路阻抗与纹波

尖峰(高频)脉冲电流,流经环路感抗时造成电源瞬间跌落,引起电源纹波

对于高频尖峰,电源路径的阻抗以环路感抗为主,加粗导线无用

-

退耦

-

对于尖峰(高频)脉冲电流,退藕环路面积小、感抗小

-

电源至退藕电容只剩低频分量,对感抗不敏感,简单加粗导线即可

-

-

退耦缓解电源线公共阻抗

退耦电容就近放置:

并非距离近,而是电容到芯片电源脚环路面积尽可能小。

干线只剩低频/直流分量,对环路面积不敏感,简单加粗降低电阻即可。

-

退耦电容的容量要求:

工作电流脉冲持续时间越长、功耗越大、电压越高,所需的电容值越大

-

退耦电容频率特性要求:

大小电容并联来保证低频和高频下都有足够低阻抗

-

电容摆放位置的要求:

退耦路径的环路面积尽可能小,比电容和芯片实际空间距离更重要

多个电容并联时,小容量的电容应更靠近芯片电源引脚

-

电源退耦的要求:

-

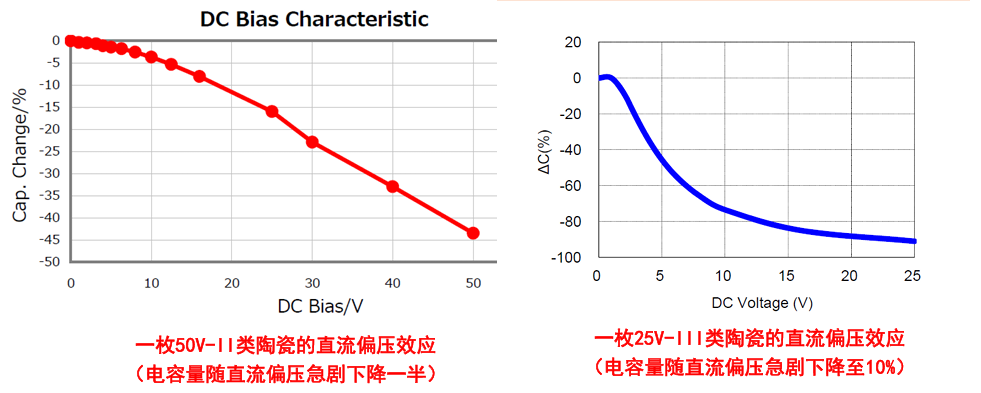

陶瓷电容偏压效应:

II-III类陶瓷介电系数随着场强增加而急剧下降,电容量也随之下降。在退耦、隔直应用时,必须在设计时考虑余量,容忍直流偏压效应引起的损失。

-

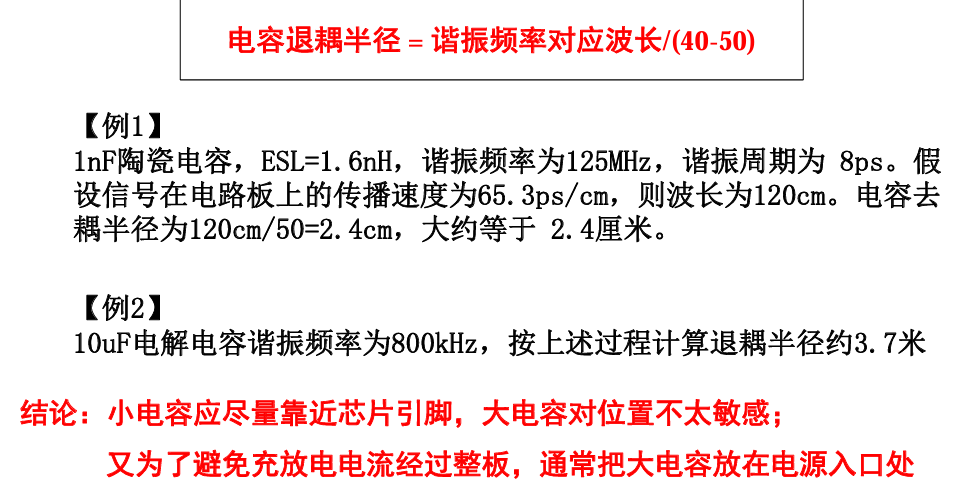

退耦半径:

-

概念:

在有完整电源平面的情况下,一个电容可以为附近的IC提供退耦 。一枚电容能够提供优良退耦效果的区域半径,称为退耦半径

-

计算:

-

-

消除寄生电感

- 就近接电源层,尽可能较少引出线带来的额外环路面积

- 不要多个电容共用过孔,会引入公共路径感抗

-

-