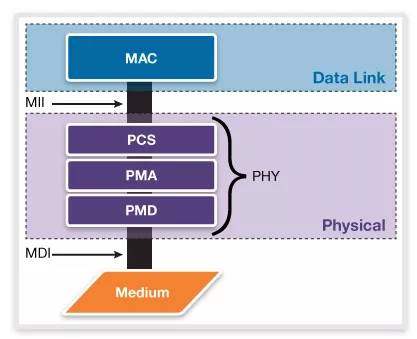

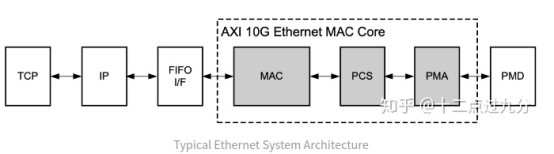

xilinx fpga中,serdes部分肯定是硬核(也可以理解为phy部分),因为serdes是数模混合的,相当于FPGA内部有一块地方是这个模块已经布局布线好了,模块的时序是得到保证的,高速的IP核自动布局布线很难达到高频下的时序要求。所以包含serdes部分的IP可以理解为硬IP,比如PCIE,PCIE可以理解包含controller,phy, phy部分就是硬的,controller可以硬也可以自己写。FPGA内的serdes ,PMA部分就是硬的(包含模拟部分),PCS可以用IP也可以自己写。所以xilinx 的pcie,或者10G eth 其实是完整的包含了PCS PMA PMD,也实现了完整的phy芯片的功能,它的物理层部分由serdes完成,部分编码,解扰码由PCS也就是IP核完成。

而DDR,一般挂在HP bank上,这是可配的,所以其实MIG不算硬IP。下面贴两张图: