微信视频号:sph0RgSyDYV47z6

快手号:4874645212

抖音号:dy0so323fq2w

小红书号:95619019828

B站1:UID:3546863642871878

B站2:UID: 3546955410049087

什么是SoC?

作为智能手机、汽车电子、人工智能、工业控制等领域的“大脑”,SoC (System on Chip, 片上系统) 是一种将计算核心、存储系统、通信接口以及各种外设集成到一个单一芯片上的高度集成解决方案。

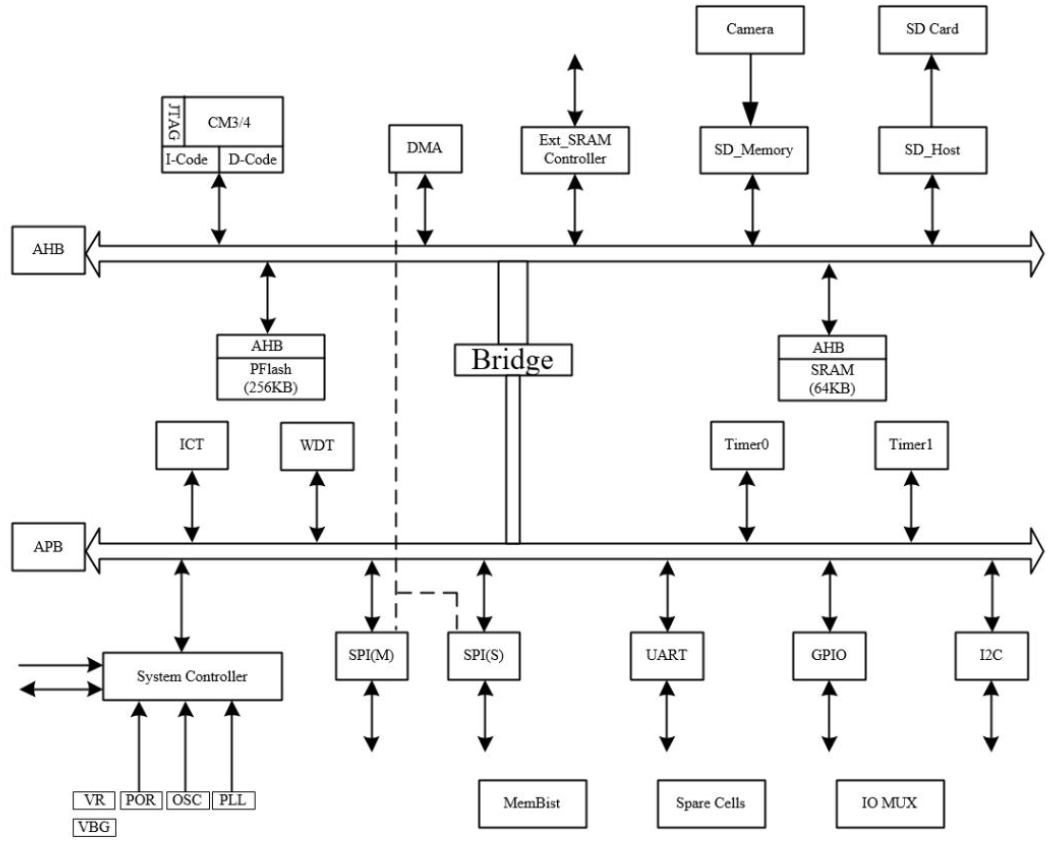

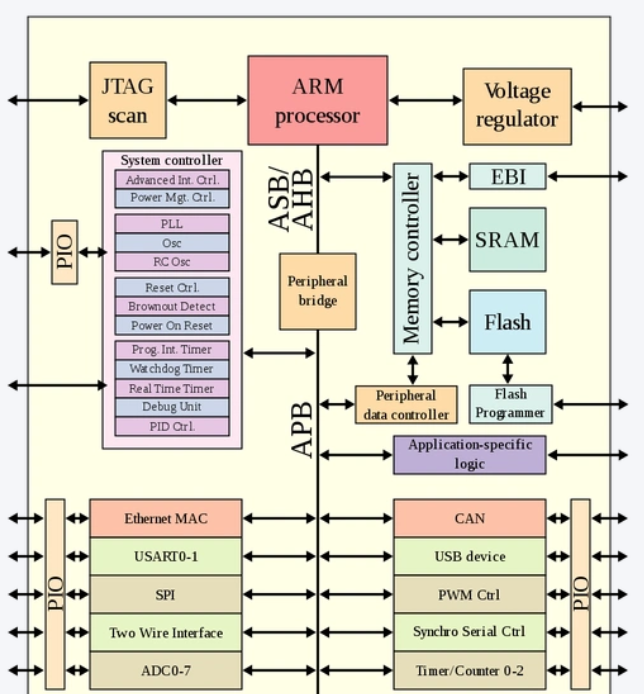

SoC架构主要包含四大组件: 1、核心 CORE 2、存储 MEM 3、外设接口 IO 4、总线 BUS

所以SoC通常包括一个或多个处理核心(如MCU内核、CPU、GPU、DSP)、存储单元(如RAM、ROM)、通信接口(如Wi-Fi、蓝牙、以太网)、外设接口(如GPIO、ADC/DAC电源)以及其他专用硬件模块。SoC的目标是将一个完整的计算系统嵌入到一个单独的芯片中,从而提高性能、减少体积、降低功耗。

典型的SoC系统级芯片结构包括以下部分:

·至少一个微控制器(MCU)或微处理器(MPU)或数字信号处理器(DSP),但是也可以有多个处理器内核;

·存储器可以是RAM、ROM、EEPROM和闪存中的一种或多种;

·用于提供时间脉冲信号的振荡器和锁相环电路;

·由计数器和计时器、电源电路组成的外设;

·不同标准的连线接口,如USB、火线、以太网、通用异步收发和序列周边接口等;

·用于在数字信号和模拟信号之间转换的ADC/DAC;

·电压调理电路及稳压器。

添加图片注释,不超过 140 字(可选)

计算核心CORE主要分为CPU、GPU、NPU、DSP:

CPU(中央处理单元)

ARM Cortex-A/R/M:适用于移动设备、嵌入式设备、实时计算。

RISC-V:开源架构,适合自研芯片。

GPU(图形处理单元)

负责 3D 渲染、游戏计算、AI 加速(如 Mali、Adreno、PowerVR)。

NPU(神经网络处理单元)

处理 AI 推理任务,如自动驾驶、智能摄像头(寒武纪 MLU、华为 Ascend)。

DSP(数字信号处理器)

处理信号计算,如音频处理(高通 Hexagon)。

添加图片注释,不超过 140 字(可选)

SoC根据应用场景,可以分为端侧SoC和服务器 SoC,端侧SoC又分为智能终端SoC,和物联网MCU SoC(或域SoC)。应用领域包括移动设备:智能手机(高通骁龙、苹果 A 系列)、平板电脑;物联网:智能家居传感器、可穿戴设备;汽车电子:车载娱乐系统、自动驾驶芯片(如特斯拉 HW4.0);嵌入式系统:工业控制、医疗设备(如心率监测仪)。

而内置了AI引擎NPU的SoC芯片,则称为端侧AI SoC芯片。其中核 CORE是CPU、GPU的为智能终端AI SoC芯片,核 CORE是MCU的为AIoT物联网终端 AI SoC芯片,或叫域控制器AI SoC芯片。

核 CORE是核心组件,其类型对整体性能有着显著影响。目前,主流的核可分为三类:CISC(复杂指令集计算机)、RISC(精简指令集计算机)以及RISC-V。CISC以x86为代表,广泛应用于PC和Server领域;而RISC则以ARM为代表,在手机芯片和嵌入式系统等领域占据主导地位。

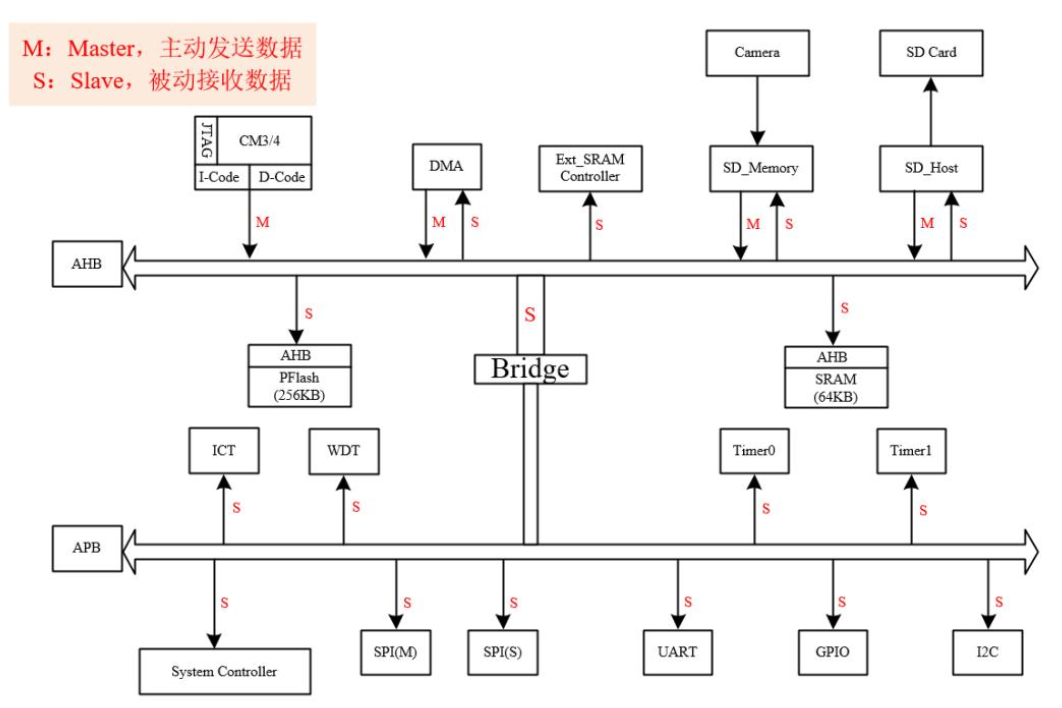

SoC核 CORE一般包括三种代码:I-Code代表指令代码,而D-Code则表示数据代码。此外,JTAG技术被广泛应用于芯片的调试过程中,以便下载和调试程序。I-Code和D-Code,即I-Cache和D-Cache,并非每个SoC都会采用,其使用与否需根据实际芯片的规模和特定需求来决定。

如某ARM架构的芯片代码分布机制如下:

添加图片注释,不超过 140 字(可选)

不同的核 CORE可以组成不同的CPU、GPU、NPU,CPU是指串行指令集算法核 CORE,主要负责工作流处理;GPU是指并行指令集算法核 CORE,一般用于数据压缩与解压缩处理,如音频、视频、文字、表格的处理;NPU是指神经网络加速指令算法核CORE ,主要运行积分矩阵算法。CPU+GPU一起的芯片叫超级芯片,NPU+CPU或GPU,就是加速算法处理AISIC芯片,也就是AI人工智能芯片,等同于CPU+GPU+NPU AI人工智能主板卡。

SoC存储架构包含下面部分:

Cache 体系:L1(指令/数据缓存)、L2(共享缓存)、L3(片上缓存)。

外部存储:DDR(LPDDR5X)、eMMC/UFS(存储芯片)。

存储单元MEM包括PFlash和SRAM两种存储器。PFlash类似于硬盘,具有掉电不丢失数据的特性。当PFlash存储空间不足时,可以通过扩展Flash,如NFC(Nand Flash Controller),来增加存储容量。SRAM作为静态随机存储器,其数据在掉电后会丢失。

与SRAM相对的是动态随机存储器(DRAM),但SRAM无需刷新即可保持数据,而DRAM则需要不断刷新以维持数据。由于DRAM的高密度特性,当需要存储大量数据时,其组成的Memory面积相对较小,因此常用于小型SoC中。若SRAM存储空间不足,同样可以通过如Ext_SRAM来扩展增加容量。

系统上电后,CPU会从PFlash中读取指令,即“软件”代码,以启动系统运行所需的程序。启动过程中,必要的代码会被下载至SRAM中,以便在SRAM中执行程序。因此,BootLoader等关键程序通常存放在PFlash中,上电后会被自动加载至SRAM中,由CPU从SRAM中取指执行。由于SRAM的存储速率高于PFlash,所以执行程序通常在SRAM中进行,而启动程序及不常用的数据则存放在PFlash中。

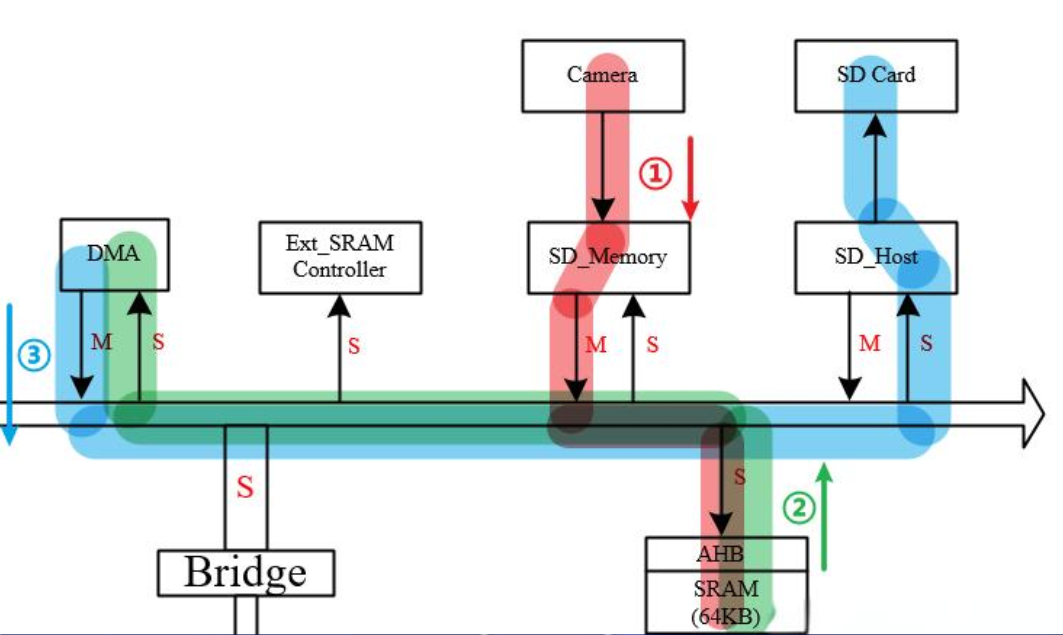

SoC系统中的其它部分叫着外设,通过总线协议与核CORE和存储单元MEM协同工作。外设IO分为两大类:高速外设IO和低速外设IO。高速外设IO,如DMA、Ext_SRAM Controller、SD_Memory和SD_Host,其运行频率达到AHB 100MHz,主要处理高速数据传输和控制任务。而低速外设IO,包括SPI、UART、GPIO和I2C,它们的运行频率为APB 50MHz,更适用于处理低速数据和通信需求。

为了更高效的吞吐更大容量的数据,SoC还会配备DMA引擎(Direct Memory Access,直接存储器访问),DMA对外并无接口,直接与CPU相连。

添加图片注释,不超过 140 字(可选)

当CPU需要从SRAM中搬移大量数据时,传统的做法是先将数据搬至CPU的寄存器,再通过取指令和写操作等方式将数据搬至目的地。这种方法不仅效率低下,还占用了CPU的宝贵处理时间,DMA引擎就是为了节省CPU搬运数据的负担。CPU只需告知需要搬移的数据量及目的地地址,DMA便会自动进行数据搬移,无需CPU的持续参与,只要发出指令就行。

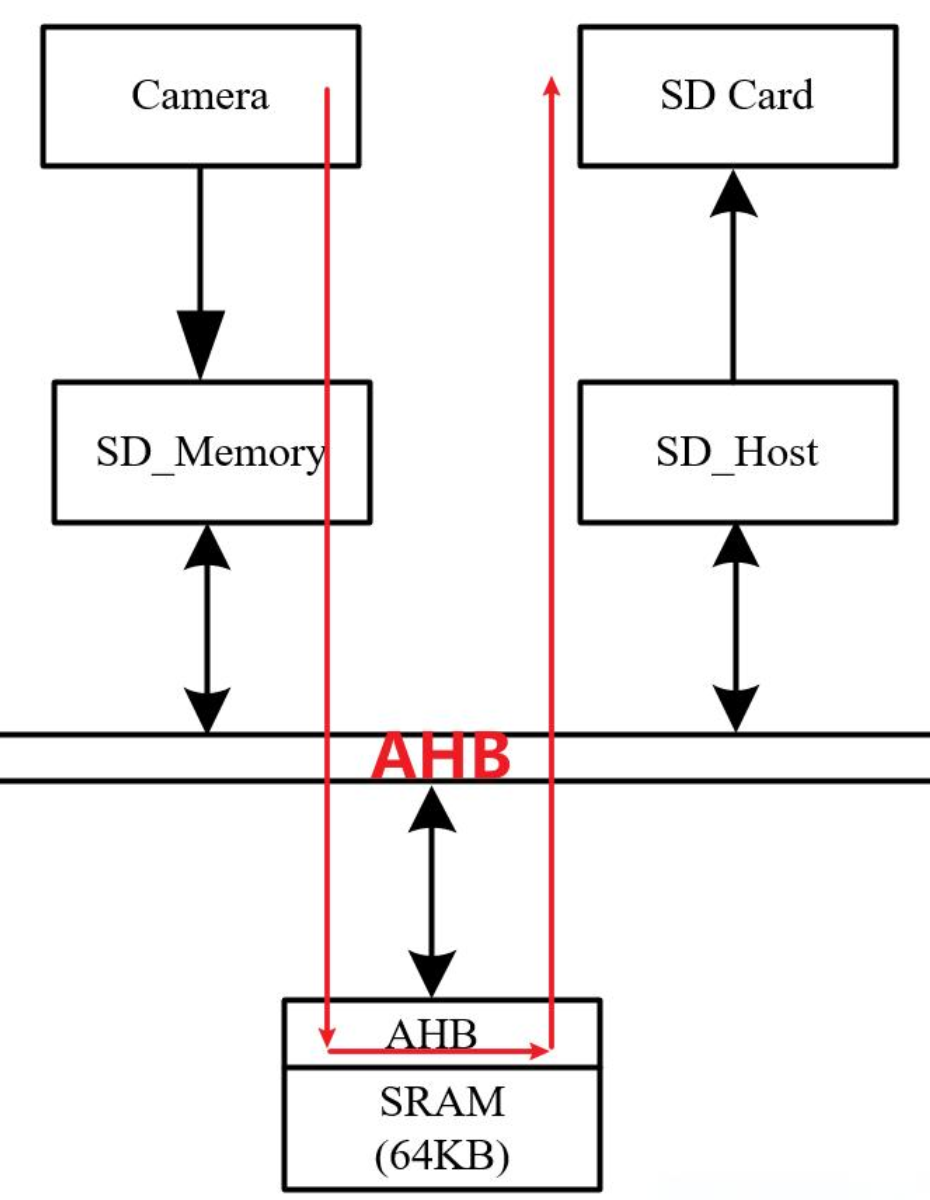

另外SoC还可以配置SD_Memory,通常与诸如Camera、麦克风之类的设备相连,用于将拍摄的影音照片、视频、音频数据通过SD_Memory接口存入SRAM。随后,SD_Host接口将SRAM中的数据进一步保存至SD卡中。

添加图片注释,不超过 140 字(可选)

SoC常见的三个低速外设接口包括I2C、UART和SPI,它们各有特点。UART接口常用于长距离传输,但传输速率相对较低,更适合点对点的通信,一个接口仅能连接一个UART Slave。I2C接口的传输速率更快,但通常不会超过特定限制,I2C还支持在短距离内连接多个Slave设备。SPI接口在速度上相较于UART和I2C更为出色,且一个SPI Master接口可以同时连接多个SPI Slave,同时也需要更多的IO资源。

当外设与核心核 CORE如CPU进行通信时,通常采用两种方式:一是CPU主动查询外设的状态;二是外设直接向CPU发送中断,CPU在收到中断后进行处理。BootLoader程序和中断处理程序是预先编写的,存储在FLASH中,系统启动后会加载至SRAM中以供使用。当中断发生时,系统会根据中断向量号查找并执行相应的中断处理程序。在数据传输中,主动发起数据的设备被称为master,而被动接受数据的设备则被称为slave。

添加图片注释,不超过 140 字(可选)

CPU通常扮演着Master的角色,作为数据的发起者。而存储系统如PFlash和SRAM,则作为Slave存在,它们被动地接收来自CPU的命令,并根据命令读取相应地址的数据。此外AHB高速外设中的SD_Memory和SD_Host模块,则兼具Master和Slave的双重功能:在SD_Memory、SD_Host模块工作时,数据通过Master口进行传输,而Slave口则主要用于CPU对其进行配置。

其它的慢速外设如SPI、UART、GPIO、I2C、Timer、WDT和ICT等,它们都通过Slave口与CPU进行交互,CPU通过配置这些外设来告诉它们需要传输的数据。包括外设接口(USB、I2C、SPI等),允许与其他设备进行通信。

外部接口包含以下部分:高速接口有PCIe(连接 SSD、扩展设备);USB 3.1/3.2(数据传输);MIPI DSI/CSI(显示和摄像头接口)。通信接口有以太网、Wi-Fi、5G 基带(高通 X70 5G 基带);UART、SPI、I²C、CAN(汽车和工业控制)。

例如,USB接口用于连接外部设备,I2C和SPI用于与传感器和其他低速设备通信,UART则用于串行通信;网络接口(Wi-Fi、蓝牙、以太网)现代SoC通常集成了无线通信模块,如Wi-Fi和蓝牙,以及有线通信模块,如以太网接口。这些接口使得SoC能够在物联网设备、智能手机、平板电脑等各种应用中与其他设备和网络连接。

此外,SoC中还会包含一些内部组件,如WDT(看门狗),一种用于监测系统状态的机制。内核会定期“喂狗”以保持其活动状态。一旦内核出现故障或挂起,看门狗计时器会溢出并触发一个中断,通知外部世界芯片已失效,需要采取措施进行处理。

Timerx(硬件计数器),CPU内部的计数器,用于测量时间间隔。通常,CPU的计数精度较低,仅能达到微秒级别,而我们的硬件计数器则可提供纳秒级别的精确度。此外,使用硬件计数器可以减轻CPU的负担,提高效率。

ICT(指令计数),用于统计指令执行情况的机制。它可以追踪和记录程序中的指令执行数量,为性能分析和优化提供重要数据。

还有一些其它组件,如包括POR(Power On Reset,即上电复位)、OSC(Oscillator,晶振)、PLL(Phase Locked Loop,锁相环)、VBG(电源管理)和VR(Voltage Regulater,电压调节器)在内的模拟组件,以及IO小模块等,这些组件都被统称为IP(Intellectual Property,即知识产权)。IP模块通常是预先设计好的、可重用的电路或系统组件,如处理器、存储器、接口等。

内部通信总线 (Bus/NOC)包含以下部分:

AXI/AHB/APB 总线

AXI(高吞吐,如 CPU ↔ DDR),AHB(高带宽,如 GPU),APB(低速,如 UART)。

NoC(Network-on-Chip)适用于多核 SoC,提高通信效率(如 AI 芯片、自动驾驶芯片)。

其它协同管理功能模块

除接口、总线、IP组件外,SoC还有许多其他关键模块。这些模块协同工作,确保SoC能够高效地执行各种任务。这些关键模块包括但不限于时钟管理模块、电源管理模块、复位管理模块以及调试接口模块等。

如MemBist技术主要针对内存模块,特别是SRAM,进行内建自测试。在芯片制造过程中,可能会引入某些缺陷,因此在芯片完成后,会进行一系列的测试以确保其质量。MemBist是一种高效的内建自测试方法。MemBist无需借助外部管脚,它通过在SRAM外部包裹一层Bist逻辑,并在内部触发使能信号,从而能够向SRAM中注入各种测试激励,并输出经过逻辑处理的激励,以此完成对SRAM的内建自测试,这就是MemBist的核心功能。

而Spare Cells通常被放置在芯片的顶层,其作用是在芯片投片后发现BUG时,能够通过ECO(Engineering Change Order,即手动修改集成电路的过程)来快速修复。在ECO过程中,可能会涉及到某些cell的替换,而预先放置的Spare Cells便可直接用于替换,从而避免了因增加新cell而可能导致的整个Die面积不足的问题,可以在不影响整个FloorPlan的情况下,高效地利用Spare Cells进行修复工作。

在售后维修中,对于一些损坏了部分cell的产品,也可以通过ECO方式屏蔽掉损坏的cell继续使用,但由于少了一些cell,功能会有所减弱,业内称这种SoC为ReMark芯片。有时候为了让少了cell的ReMark芯片功能与原厂芯片差不多,一些商家会对cell进行超频,让其发挥更强的功能,但有可能会提高芯片的功耗和发热量,这些产品业内就戏称为“发烧级SoC芯片”。

引脚接口管理系统

另外SoC还包含有与外界互联的引脚接口管理系统,如PAD引脚分配区则是具体实现引脚与芯片内部电路连接的区域;Pin-MUX引脚复用器,负责将单一的物理引脚映射到多个逻辑功能上,从而实现引脚资源的灵活配置。

PAD包括Input Only、Output Only和Bidirection三种类型。Bidirection类型的PAD最为常用,通过控制EN信号,可以灵活切换其输入或输出功能。此外一些SoC还存在模拟PAD,如LVDS,以及VR(电压调节器)PAD等特殊类型的PAD。

PAD作为芯片与外部通信的重要接口,承担着数据传输与交换的关键任务,Pin-MUX则能够有效地减少PAD的数量。通过这两大组件的协同作用,SoC架构能够高效地管理引脚资源,为芯片设计带来更大的灵活性和可扩展性。

添加图片注释,不超过 140 字(可选)

上面这些一起,就组成了完整的SoC芯片。

添加图片注释,不超过 140 字(可选)

SoC需要哪些IP组件、通讯协议和控制端口,主要由芯片设计来完成。SoC设计流程

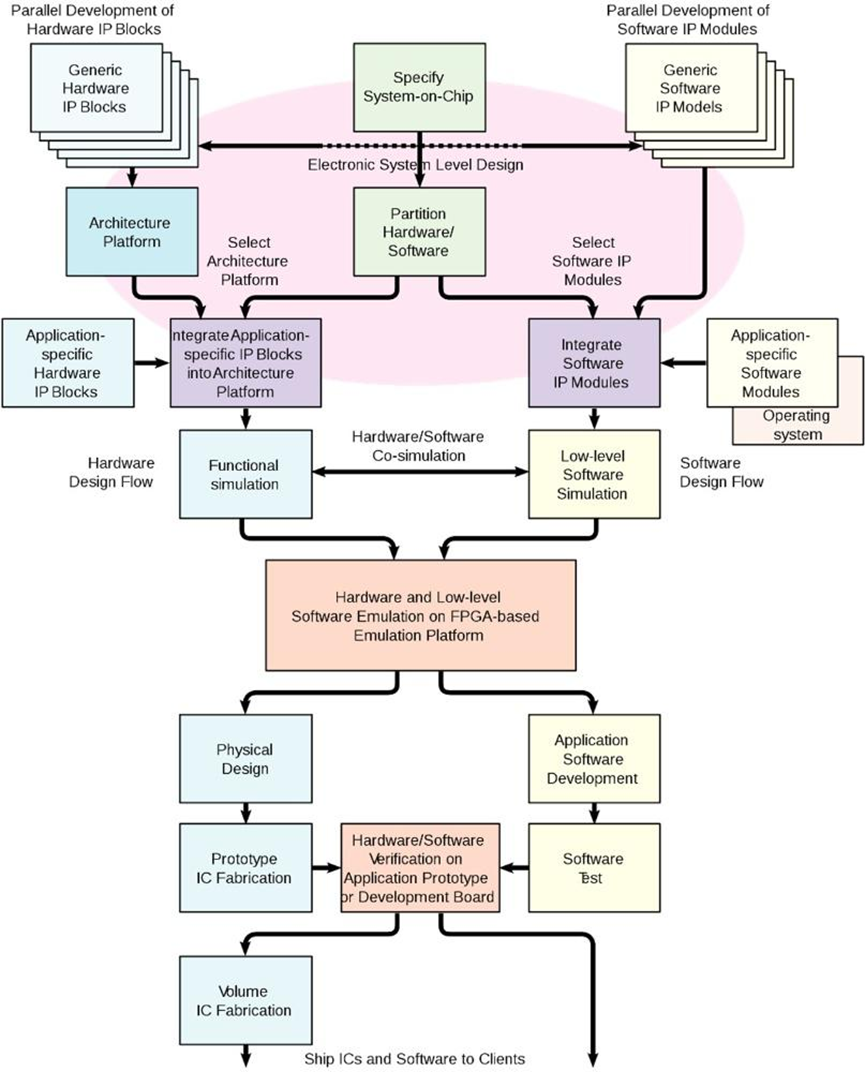

一个完整的系统级芯片由硬件和软件两部分组成,其中软件用于控制硬件部分的微控制器、微处理器或数字信号处理器内核,以及外部设备和接口。系统级芯片的设计流程主要是其硬件和软件的协同设计。

由于系统级芯片的集成度越来越高,设计工程师必须尽可能采取可复用的设计思路。现今大部分SoC都使用预定义的IP核(包括软核、硬核和固核),以可复用设计的方式来完成快速设计。

在软件开发方面,协议栈是一个重要的概念,它用来驱动USB等行业标准接口。在硬件设计方面,设计人员通常使用EDA工具将已经设计好(或者购买)的IP核连接在一起,在一个集成开发环境(IDE)下集成各种子功能模块。

添加图片注释,不超过 140 字(可选)

系统级芯片的设计流程示意图。(来源:维基百科)

芯片设计在被送到晶圆厂进行流片生产之前,设计人员会采取不同方式对其逻辑功能进行验证。仿真与验证是SoC设计流程中最复杂、最耗时的环节,约占整个芯片开发周期的50%~80% ,采用先进的设计与仿真验证方法已成为SoC设计成功的关键。

添加图片注释,不超过 140 字(可选)

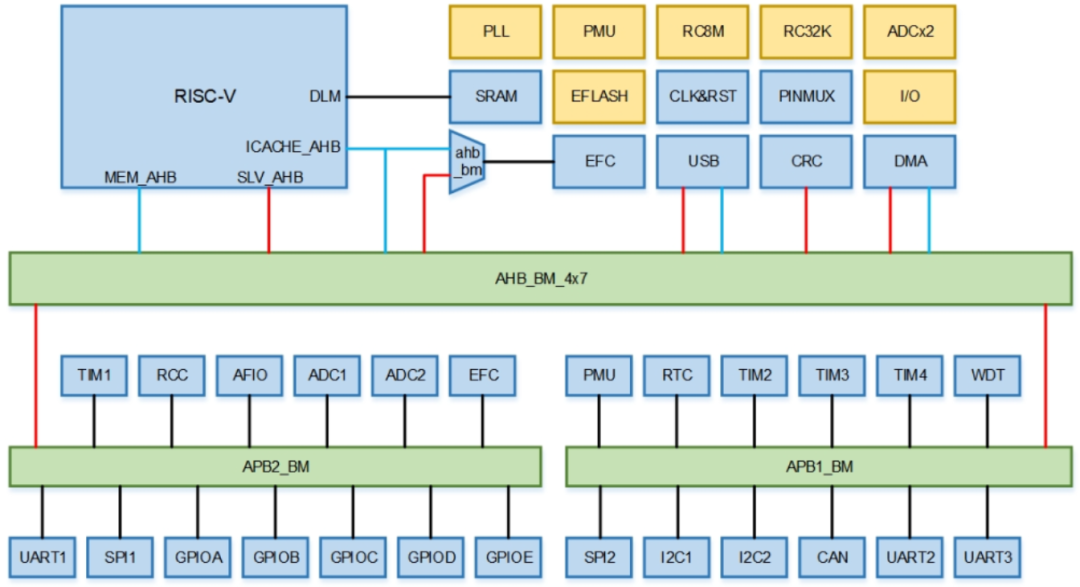

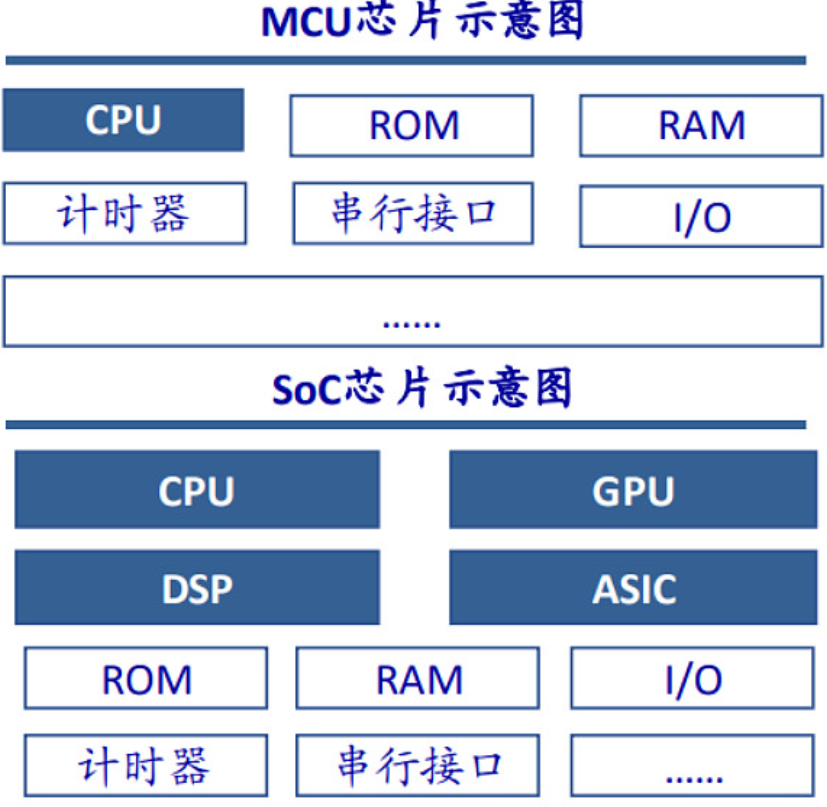

而MCU SoC是以 MCU芯片作为核心CORE基础上增加总线协议,再把核心CORE、内存管理系统,通过总线协议与音视频管理系统、电源管理系统、蓝牙/Wifi及其它通讯协议管理系统独立出来进行增强,再集成在一起的片上系统,主要是为了弥补MCU算力满足时,在数据采集与传输方面的短板。

其中MCU(Microcontroller Unit),即微控制器,又叫单片机,是把CPU的主频与规格做适当缩减,并将存储器、定时器、A/D转换、时钟、I/O端口及串行通讯等多种功能模块和接口集成在单个芯片上,实现终端控制的功能,具有性能高、功耗低、可编程、灵活度高等优点。

添加图片注释,不超过 140 字(可选)

添加图片注释,不超过 140 字(可选)

如最简单51内核MCU的内部组成,有CPU、RAM、ROM、定时器(计数器)、串口、外部中断组成。

添加图片注释,不超过 140 字(可选)

如RISC-V架构的MCU,主要由下面这些部分组成。

添加图片注释,不超过 140 字(可选)

如ARMv7架构Cortex-M3内核的STM32,内部组成会更复杂。

添加图片注释,不超过 140 字(可选)

MCU一般最多只运行实时操作系统(RTOS),主要采用“裸机”编程。

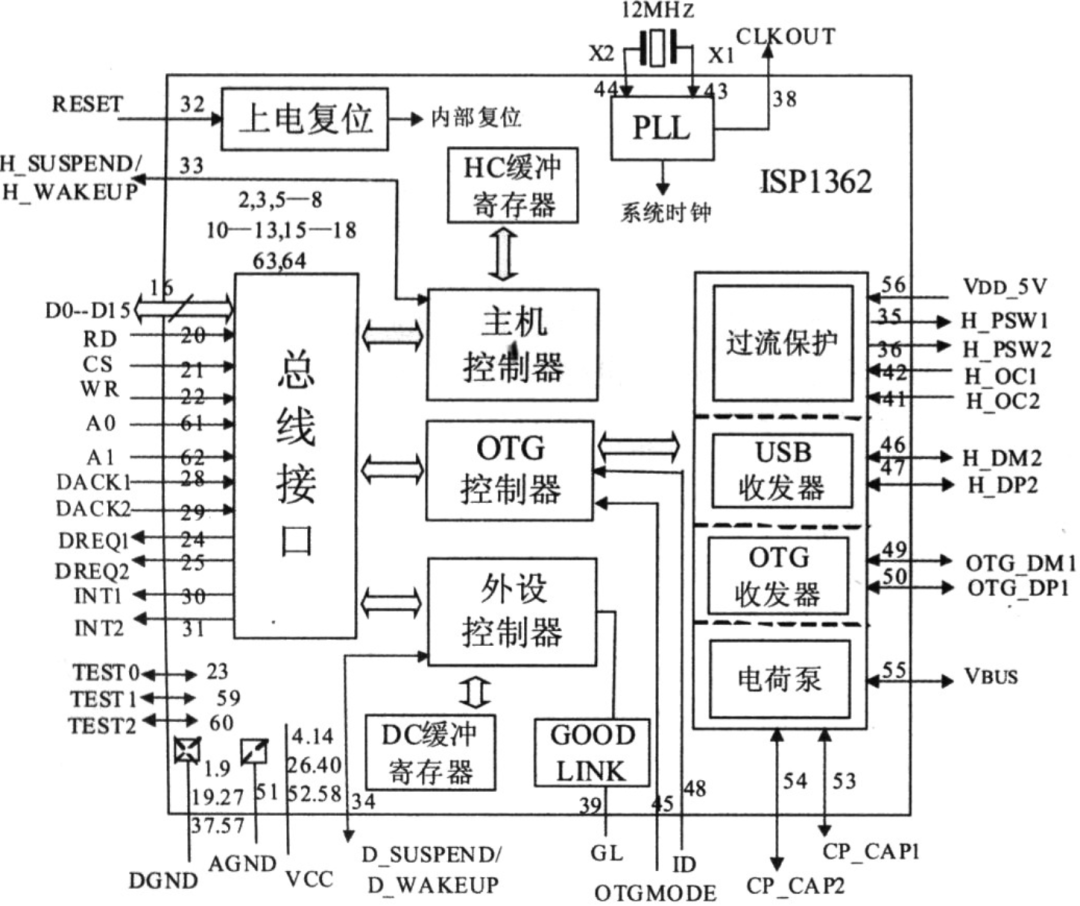

而随着数据传输的容量越来越大,传输的带宽越来越宽,很多原来属于MCU和SoC的单个功能模块,也开始设计成MCU单元,包括电源管理芯片、射频通讯芯片、数据传输接口芯片等,如下面的USB 2.0总线协议的接口芯片,内部有3个USB控制器一主机控制器、设备控制器和OTG控制器:

添加图片注释,不超过 140 字(可选)

添加图片注释,不超过 140 字(可选)

另外业界还有一种分类叫MPU (Micro Processor Unit),也叫微处理器,是可编程特殊集成电路。MPU只是一个处理器,需要搭配内存等非常多的其他四外设才可以构成一个系统。与之相对,MCU内部有处理器、内存、Flash及其他模块,仅仅需要搭配少量外设就可以构成一个系统,

MPU在上世纪80年代非常流行,那时的微型计算机,游戏机都是使用MPU,比如Motorola公司的68000芯片就是一款主流的微处理器(MPU).下图是一款Alpha Micro AM-1000系列的微型计算机电路板,电路板右侧中间最大的芯片就是MPU 68000,

后来MPU逐渐式微,可以认为MPU发现到现在只剩下了inteL、AMD公司x86系列CPU,这类CPU也越来越复杂,称之为“微处理器”似乎不恰当了。在个人电脑领域,可以看到类似下图的主板。主板上插上CPU、内存条、声卡等等就构成了一台计算机。整个主板体积庞大、制造复杂。

MPU与MCU的区别在于微控制器 (MCU)往往比微处理器 (MPU)更便宜、设置更简单、操作更简单。MCU可以被视为单芯片计算机,集成了ROM、RAM等在芯片内部,而MPU则具有支持各种功能(如内存、接口和I/O)的外围芯片,可任意更换不同厂商的同种类型外设。微控制器和微处理器之间的一个重要区别是微处理器通常会运行操作系统。操作系统允许多个进程通过多个线程同时运行。需要驱动程序来支持外围设备。

随着MCU集成的外适功能越来越多,要判断一个设备是 MCU还是 MPU也变得越来越困难。因为如今 MCU可以做很多事情,包括更复杂的外围设备,MCU和 MPU之间的区别也变得不那么明显,现在一些 MCU带有用于更复杂外设的简单软件驱动程序越来越象MPU,同样也可以找到更多具有片上集成外设的 MPU,能实现MCU的功能。

而SoC是系统级芯片,可包含许多MCU,作为一个完整的单芯片计算机系统,能够执行具有更高资源需求的复杂任务。

添加图片注释,不超过 140 字(可选)

低端的SOC就是内部集成了MCU+特定功能模块外设,也就是MCU SoC,集成了NPU的MCU SoC就叫AI MCU SoC。高端的SoC是内部集成MPU/CPU+特定功能模块外设,也就是常说的普通端侧SoC、服务器SoC,AI SoC等SoC芯片了。

添加图片注释,不超过 140 字(可选)

其中SoC是System on Chip,整体的一个电路系统,完成一个具体功能的东西,指的是片上系统,MCU只是芯片级的芯片,而SoC是系统级的芯片,它既MCU那样有内置RAM、ROM同时又像MPU那样强大,不单单是放简单的代码,可以放系统级的代码,也就是说可以运行操作系统(以Linux OS为主)(将就认为是MCU集成化与MPU强处理力各优点二合一)。

另外还有SoPC(System On a Programmable Chip),与上述几项概念相比,SoPC的出现频率并不是那么高,但这并不影响它的重要性。SOPC是System On a Programmable Chip的缩写,即可编程片上系统,SoPC与MCU、MPU、SoC最明显的区别在于:可更改硬件配置,也就是说自己构造芯片。

通俗点讲,MCU单片机的硬件配置是固化好了的,能够编程修改的就是软件配置,来选择其中的一项或多项功能;而SoPC可以修改硬件配置信息使其成为相应的芯片,可以是MCU,也可以是SoC。

而随着NPU IP核的成熟,越来越多的传感器也开始跟传感器的DSP芯片(数字信号处理器芯片)进行集成,同时植入NPU IP内核和其它的周边通讯协议、射频等IP内核,甚至整个完整的MCU功能往智能传感器方向升级;同时一些通讯网卡产品,也开始集成NPU IP核和MCU完整核,往智能网卡方向升级;另外,电源管理芯片行业也在研发自己的NPU IP核,以实现按需预调峰,达到智能稳压、稳流功能等,也就是大部分芯片的数字化部分,都会启动特征码的压缩与解压算法研发,以达到数字化与智能化结合,生成新的AI芯片架构与产品。

基本上,算力芯片从简单到复杂,再到智能化的路线为:CPU、MPU、MCU、SoC、SoPC、AI DSP、AI SoC,未来或许还会有AI SoPC……

微信视频号:sph0RgSyDYV47z6

快手号:4874645212

抖音号:dy0so323fq2w

小红书号:95619019828

B站1:UID:3546863642871878

B站2:UID: 3546955410049087

参考文献链接

一文看懂AI SoC芯片