初来乍到,先自我介绍,我是一所双非学校集成电路专业的学生,目标是成为一个合格的FPGA,数字ic设计,验证工程师,目前大三,此篇章仅以记录我打FPGA创新创业大赛过程的一些学习经验,是基于zynq7020开发板的开发项目,希望能让小白们更快学习,大佬们认可和指正,也希望自己能在后面忘记某个知识点时能翻阅来找思路与bug。本篇章基于zynq厂商给的例程资料进行学习然后重构,有需要资料的可以私聊我,或者是直接找板子客服要就行。

继在某dn发布后朋友说有可能莫名其妙被设置为仅vip可看,因此决定转博客园继续记录。

废话不多说,延续上一节,已经知道了axi各组件的作用,以及视频流传输的各模块的一些接口有什么用(可能讲得有点粗),这节会在连线的基础上,更深入的去看每个硬件可以干嘛,怎么配置。

平台:win11,软件:vivado2017.4(官方推荐2018.2,2017有bug)

分为两个部分,数据通路和时钟复位域,先讲数据通路:(在这个部分我咨询过老师,除了需要掌握这个通路外,还需要学习各个协议与外设之间的接口,最好手撕,这里我先用官方自定义ip核,后面找机会把这块补上来)

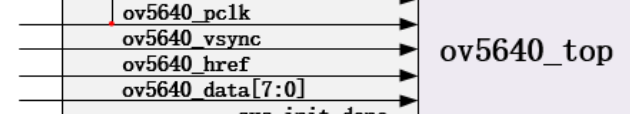

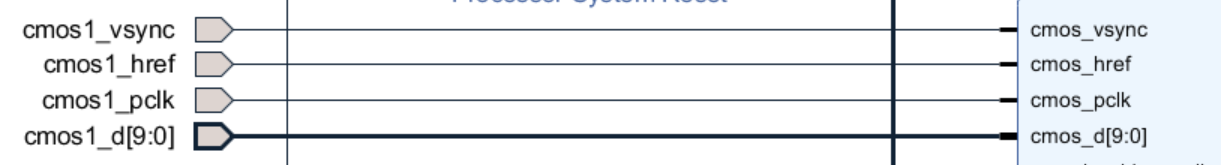

首先我们要了解摄像头的输入,根据野火教程可以知道:摄像头ov5640的输入有摄像头模块的时钟pclk,行场同步信号href,vsync,数据信号data[7:0]

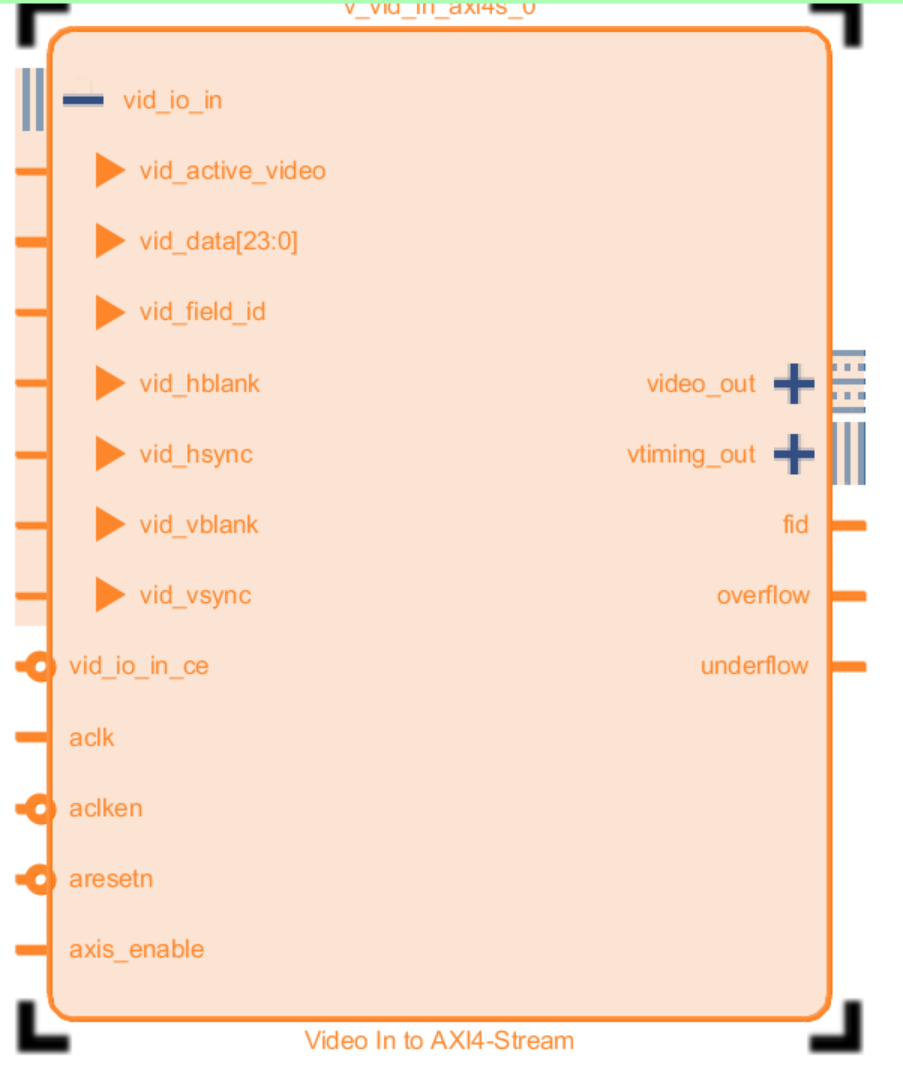

这些输入是不规范的视频信号输入,规范的还需要消隐信号(blank),id(标明是哪段视频流,类似于地址映射),以及视频的有效信号(active_video)和24位宽的数据。

但是ov5640我们的寄存器配置就是要两个数据拼接成一个16位宽的数据(RGB565),然后通过低位补0转换为24位宽(RGB888,符合HDMI标准),因此注定这中间的转化不能直接用Video in to AXI4-Stream模块进行转化,官方就写了个自定义的ip核,利用fifo完美地将ov5640信号转为axis协议输出(感觉很多接口都是用fifo,学会这个真能走天下,至少本科阶段够用,工作时会用其他的)。

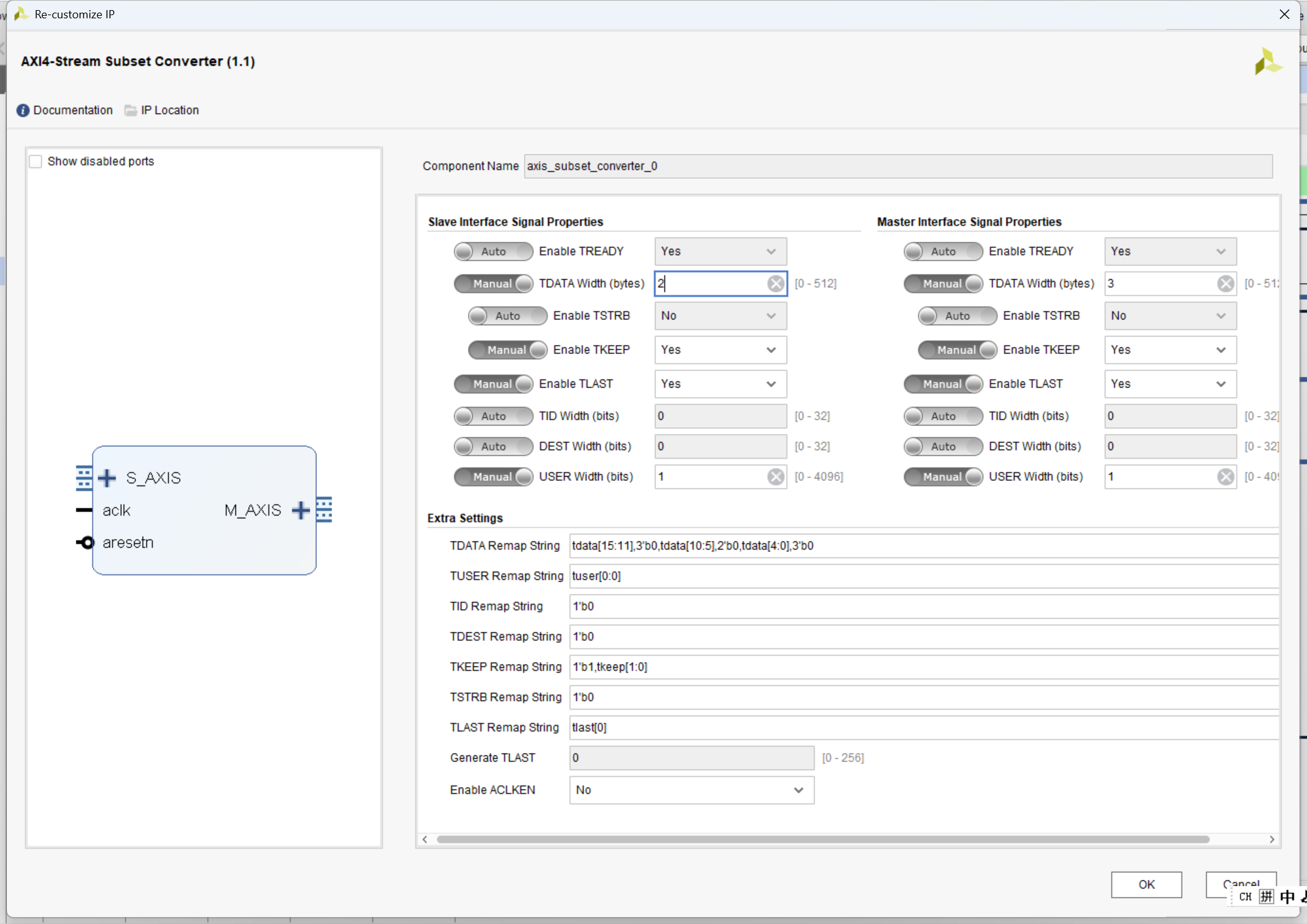

但是官方自定义ip依旧只有16位宽输出(因为只是拼接两个数据后输出,这样泛用性会强一点),然后要通过AXI4-Stream Subset Converter模块修改数据位宽,当然不能简单的高位补0,必须要了解RGB565和RGB888分别是什么意思,RGB565是相当于在一个16位宽的数据中,Red权重为最高的5位,Green权重是中间6位,Blue是最低的5位,加起来是16位,所以是RGB565,十六位宽,2字节。RGB888同理,因此由于2字节转3字节中Red在前者只有五位宽,后者有8位宽,因此要让Red低位补3个0让他变成8位宽。

这是该模块配置,左边是输入(被作为从机输入了),这个看官方ip核最后引出哪些信号,然后把它给加上就行。然后看TDATA Remap String那行逻辑就是我们说的565转888,Keep信号的话类似于Strb字节使能信号,3字节就有三位宽的数据,因为这里我们一直让数据有效,所以keep信号默认高位为1,低位按照输入的来就行。

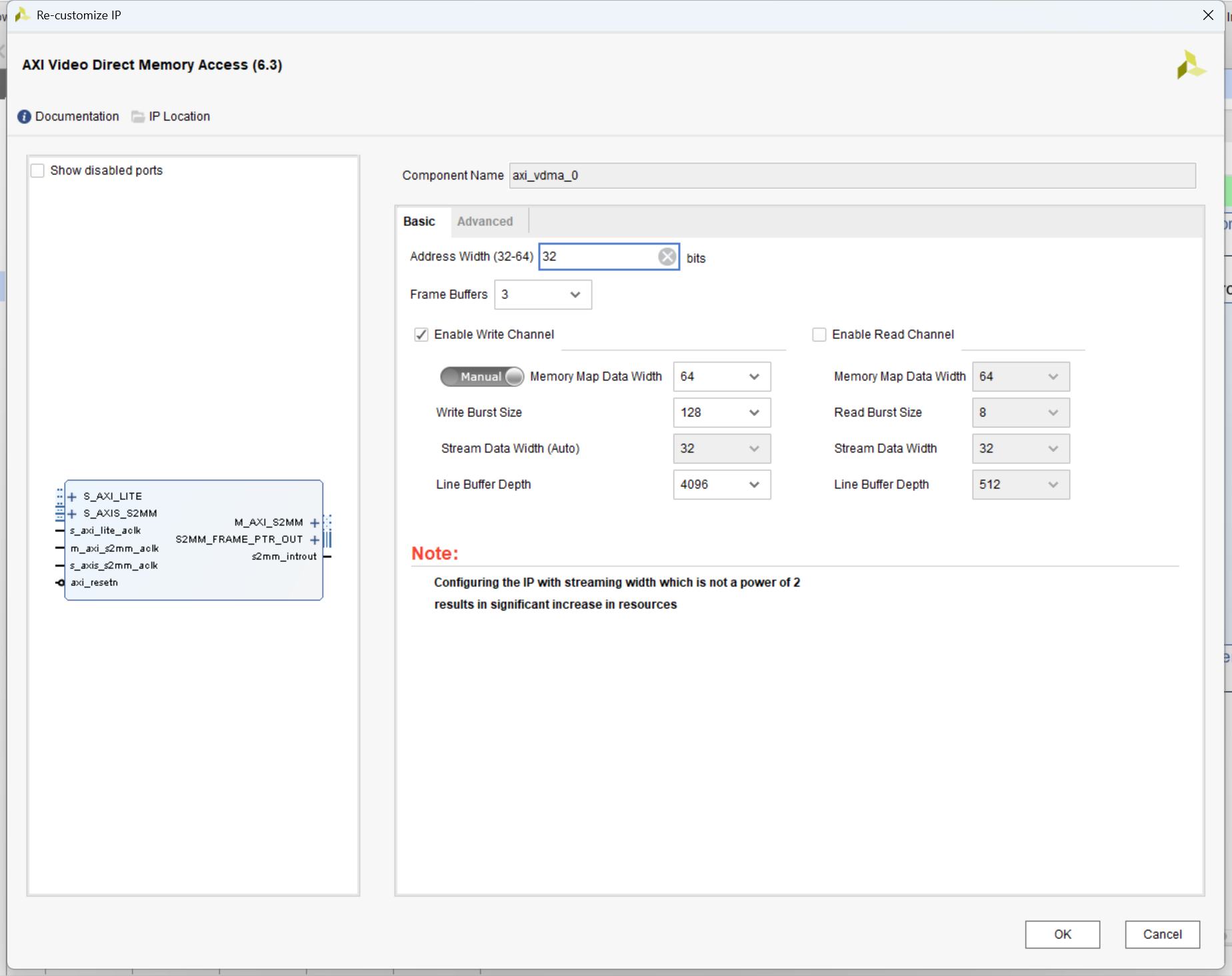

那么数据转位宽后,因为输出依旧是按照AXIS协议,所以需要一个DMA来转为AXI4协议以便和PS端交互,但是zynq有更适合视频流信号的模块AXI VDMA模块,功能更多更专业,我们用这个.

这里配置的话,帧缓冲可以设置为3会比较好,但是我这里写1,接着这个模块它会作为从机被写入,作为主机往ddr3写入数据,所以使能写通道即可,写突发长度适宜即可,Memory Map Data Width不必和输入位宽一样,因为内部有fifo,64位宽会自动填充,然后按照24位宽依旧输出,不会打乱顺序的,然后这里是2017.4的一个bug:无法自适应我输入的24位宽,官方说2018.2更正了这一bug,并且2018.2是最后一个有SDK的版本,所以会比较推荐。

之类的话Fsync Option应该就是DMA没有的,可以通过不同的模式去判断是否达到一帧,有user,none,fsync三个选项,这里要和官方自定义ip适配,必须用user,可以看到前面的axis中有tuser信号,溯源可以发现是由垂直同步信号控制,由HDMI接口协议可以找到,Vsync是垂直同步信号在每帧开始会拉低,结束会拉高,所以官方那个tuser代表着每一帧的开始,而这里的mode就代表着帧切换的模式,user就是由tuser控制,none就是不控制,fsync就是其他信号来控制,那么这里选择user模式,然后Genlock Mode选择Master即可,输出当前帧数指针,最后打勾,支持非对齐传输(可能因为如果没有CPU配置,那么地址递增不会在帧的最后进行对齐传输,所以这里用非对其防止漏数据)。

VDMA模块转完变成AXI4协议,而PS端的HP端口是AXI3协议,因此需要interconnect来转协议(后面由于需要再把数据传给下一个VDMA,所以设置为两主一从模式(从机指PS端,因为它不仅要被摄像头写入,还要被HDMI读取),然后就直接连接上PS的HP0接口,然后依旧通过互联模块转到VDMA,这个VDMA配置参考前面的,但是最后的模式设置需要改为none,因为此时并没有一个信号能告诉VDMA切换帧了,然后这里要说的一点是开通读通道相当于(噢这个VDMA还要开启读通道),数据通路为MM2S,虽然可能会以为往HDMI那边写入数据应该是写通道,实际上它是告诉我们这个数据来源于Memory Map,也就是DDR3,发送至从机,所以哪怕这里有写操作,也是读通道环节之一.

之后这个数据就要写向AXI4-Stream to Video Out模块了,就是AXIS转视频流标准输出的一个模块

可以看到有Video in和Vtiming in其中我们应该将数据通道AXIS协议接入Video in,代表传输数据即可,但是HDMI输出也需要垂直同步信号和行同步信号啊,甚至可能需要消隐信号。这里mode选择master会导致该模块自动生成适应HDMI的视频流接口,而不依赖来自外界的VTC,当然,一般来说VTC+AXIS to Video是最好的,VTC会告诉VDMA什么时候该传输数据,当然这些是HDMI显示部分的内容了,有兴趣可以自己去了解ps端是怎么让VTC来控制VDMA的,反正我没兴趣哈哈哈

接下来视频流接口还是得转为HDMI输出(各种差分信号),官方依旧给了自定义ip,所以直接用就行了,有兴趣也可以自己去写一个视频转HDMI接口,也是听有挑战的。

接下来是VTC,涉及到HDMI传输简单说下功能就行,通过ps端控制后生成每帧的同步时序,然后控制VDMA同步输出即可。

还有AXI4—GPIO模块,这个很简单,通过ps端控制是拉高还是拉低就行,对应摄像头模块的coms_rstn管脚。

然后ps端需要进行控制的有五个模块,两个VDMA,一个VTC,一个GPIO,一个MMCM,MMCM后面会讲到,可能你会想VDMA我不是配置好了吗,为什么还需要ps进行配置。大家可以回顾一下,VDMA的配置是不是没有每帧分辨率这些东西,按ai的话来说,我们在block design的配置是静态的,生成bit后无法改变,ps端是改变VDMA内部的控制寄存器来动态控制一些参数,比如分辨率,行步长,所以还需要ps端的GP(不那么高速的接口)去连接,这个接口是AXI-lite接口,由于需要连接多个,依旧用互联模块把它和其他五个从机连接起来,你会发现VDMA有S_AXI_lite,VTC有ctrl,MMCM有s00_axi,GPIO也有接口,都是满足lite协议的,这些接口就是想让ps端来控制他们的。

那么数据通路的讲解到这里就结束了,官方自定义ip核和HDMI部分讲得比较粗略,因为HDMI我一般只是用它,没想着去配置它,希望大家海涵。

接下来讲时钟复位域:(这里基本人均fifo,所以处理CDC问题很简单,我们只需要把时钟复位线接对就行,当然了如果褪去block design ,一个好的fifo,或者是握手协议,依旧是解决CDC问题的好方法),首先我们可以系统时钟我们可以引进外部晶振(50MHz)或者是让ps自己产生(ps在硬件配置支持这个功能),我们生成两个时钟,一个100MHz作为参考时钟,一个142MHz(后续会讲为什么是142M)

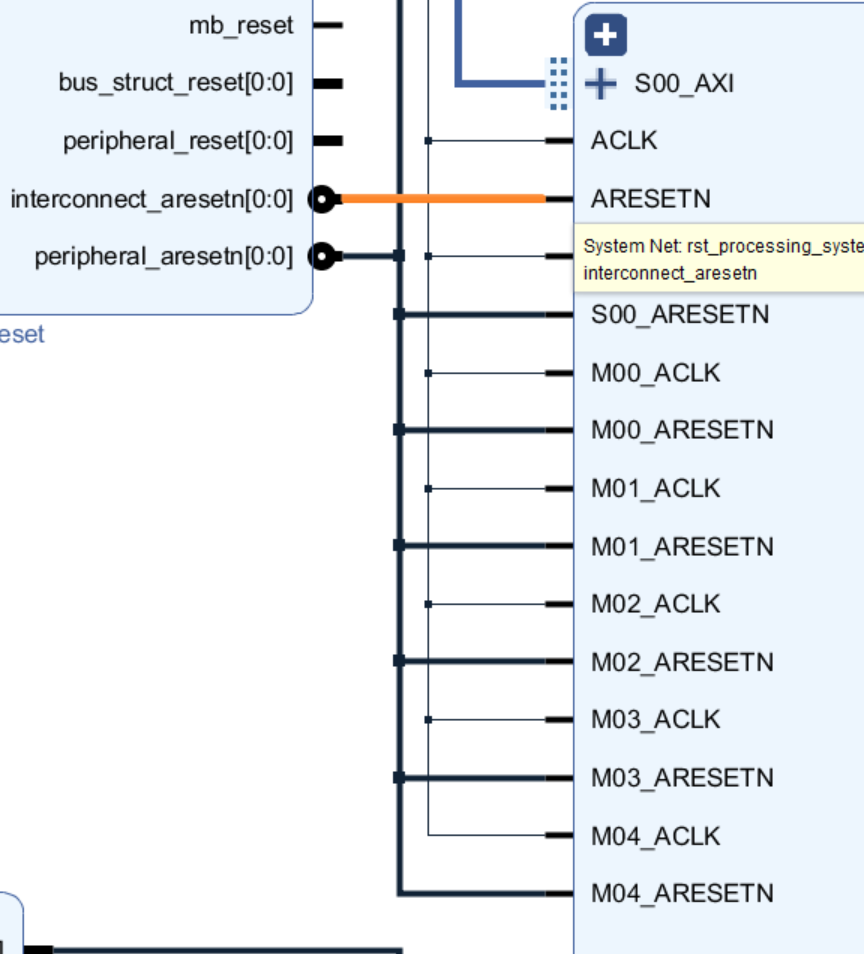

这个100MHz只是用于让ps配置控制寄存器,没有其他功能,这么说都知道怎么连线了吧,然后由于MMCM的分频需要一个参考时钟,这里官方用100M我们跟一手,然后搜下Reset,生成Processing那个复位模块,点进去把exit复位使能改为低电平有效(如果改不了,就外接非门或者是const模块),然后连接FCLK_resetn(ps端),并且把100MHz连接给这个复位模块的slowest clk(其实就一个时钟输入),这个复位模块的话输出有四个,互联模块低电平有效,外设低电平有效,互联高电平,外设高电平(其实还有,但是我们只关注这四个),由于基本模块们都是低电平有效,所以高电平复位信号没用,至于互联复位和外设复位有什么区别,一般来说互联模块会需要复位提前点,外设不用那么快(在系统设计中养成良好习惯),所以把互联模块的(记住一定是要接100MHz时钟配置控制寄存器的那个互联,不是数据通路的互联!)复位信号

如图,就接这个就行了,其他的配置控制寄存器相关的复位全部接外设复位。

接下来讲数据通路的时钟142Mhz,由于我们在ps端会去配置成1080p,可以上网搜一下发现应该是148MHz(对于HDMI输出来说),所以这条通路需要都是这个频率的数据流,但是又因为VDMA只传输有效信号,也就是说消隐时间不算在VDMA传输的时间内,所以可以稍微低一点142M,至于为什么是142,可能是因为分频精度比较高?反正不管怎么说,官方这么说,哈哈哈,而且也不用担心,频率没差太多最多漏一点数据,VDMA可是有帧切换的,不用怕上一帧的数据影响到下一帧,这可能就是它的优越之处吧。

好了接下来除了视频信号转HDMI,全部时钟都用142M,因为这是命令!因为这是数据流传输的速度,当然了一开始的pclk就不用连接,这是摄像头输入,摄像头的数据传输速率,不是我们自己的。复位的话原则和上面一样不做赘述。

接下来就是一些细枝末节了,例如converter的复位可以一直拉高,因为这种小模块不用初始化一直工作是没事的,不要说有数据进来后还不工作就行。

然后官方是有连接两个中断信号给ps端的,但是我看了ps端并没有处理中断服务,也没有开启中断的配置,所以应该是不用连接的。

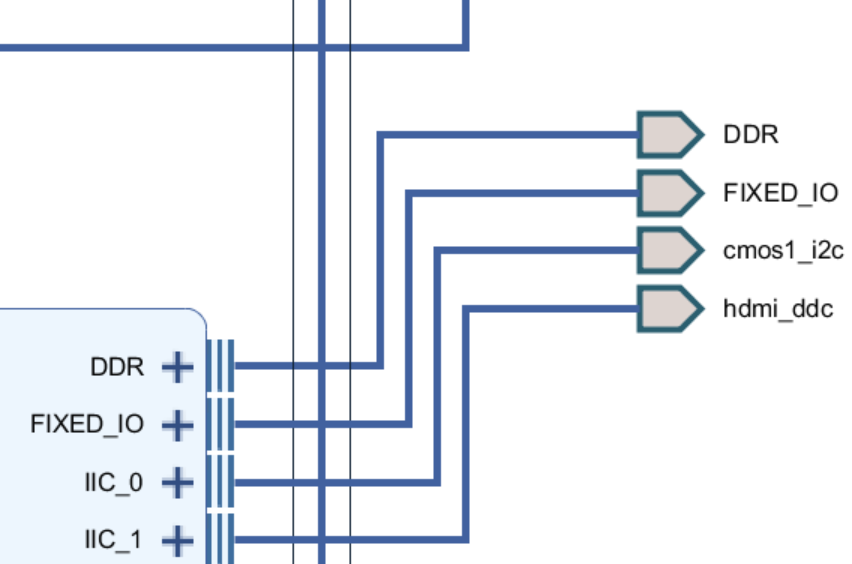

ps端记得要有一个iic接口,以配置cmos的内部寄存器(scl,sda),要配置成emio,这样才能通过约束文件绑定管脚,不然会被分配到板子上原有的iic接口上。其他的就是没连线的东西

这几个接口cteate port然后按需配置就行了,时钟记得配置成clock mode。噢不要忘记了HDMI输出TMDS。

纪录片到这里结束,祝您生活愉快。