在复杂 SoC 设计中,总线死锁是一类严重影响系统可靠性的问题:多个模块因相互等待资源而陷入永不响应的“僵局”。本文介绍先进的验证策略,结合具体案例,帮你系统掌握如何早期发现并避免总线死锁。

1、什么是总线死锁?

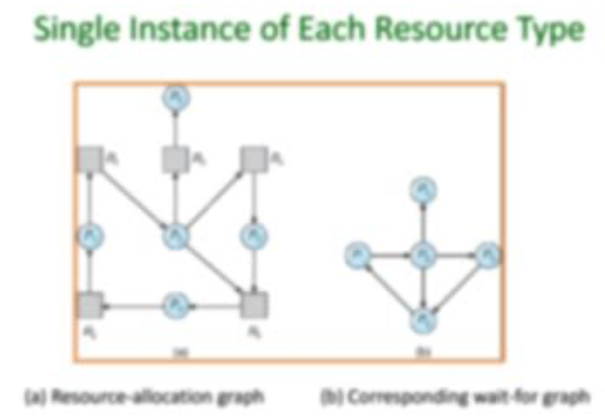

当多个组件互相等待彼此持有的总线资源,形成循环等待,导致系统无法继续操作,这就是总线死锁。尤其在多核、多请求源的环境中,检测并解决死锁至关重要。

2、验证技术详解

I. 形式验证(Formal Verification)

采用形式验证工具(如 Cadence JasperGold),通过状态空间穷举实现死锁检查。

实践案例:某半导体企业通过 JasperGold 对 NoC 总线进行形式验证,识别潜在死锁场景,并提前在设计阶段进行修复,有效提升验证覆盖率与效率。

实现要点:构建完整状态空间、定义死锁不应出现的属性,使用形式验证自动证明系统不存在死锁。

II. 仿真验证(Simulation-Based Verification)

通过仿真执行多样事务序列,捕获形式方法遗漏的死锁。

实践案例:汽车 SoC 厂商利用 Synopsys VCS 脚本模拟不同交通模式,在复杂边界条件下成功发现罕见死锁问题。

实现要点:构建测试脚本、覆盖各种事务情景,并分析仿真覆盖率以补全验证短板。

III. 混合验证(Hybrid Approach)

将形式与仿真验证结合,兼顾全覆盖与实用场景。

实践案例:数据中心处理器设计团队结合 JasperGold 和 VCS,创建协同验证流程,实现全面覆盖与快速迭代。

实现策略:先用形式快速验证全局死锁属性,再用仿真测试边界与高风险场景,确保万无一失。

IV. 机器学习辅助验证(ML-Assisted Verification)

通过历史验证数据与模型预测,智能识别潜在的死锁序列。

实践案例:某 5G 基带芯片团队采用机器学习算法分析仿真数据,预测可能发生死锁的事务路径,并优先验证这些高风险场景。

实现方向:收集仿真数据、训练模型预测死锁高风险路径,从而优化验证策略并提升效率。

3、技术亮点一览

验证方法 核心优势

形式验证 全面检查系统死锁安全性,覆盖所有状态

仿真验证 捕获实际事务模式下的罕见死锁场景

混合验证 综合优势,平衡覆盖全面性与真实可用性

ML 辅助验证 智能预测,聚焦高风险路径,有效节约验证资源

4、为什么选择 EDA Academy 学习更多?

若你希望系统掌握总线死锁验证策略,包括形式验证、仿真脚本构建、混合流程规划及 ML 优化等,推荐访问 EDA Academy(www.eda-academy.com):

海量专业课程:涵盖总线死锁验证、高级形式验证、UVM 环境搭建、仿真优化等实战内容。

成为导师的机会:你可以在平台注册为导师,分享验证经验,提升行业影响力。

免费订阅技术资讯:邮箱注册即可获得最新验证技术动态与干货推送。

销售联盟计划:推荐课程给同行即可获得 20%–50% 佣金,让学习增值。

通过形式 + 仿真 + ML 验证组合,再辅以 EDA Academy 的专业课程引导,你将成为总线死锁验证与可靠性提升领域的技术高手。立即行动,开启专业成长之旅!