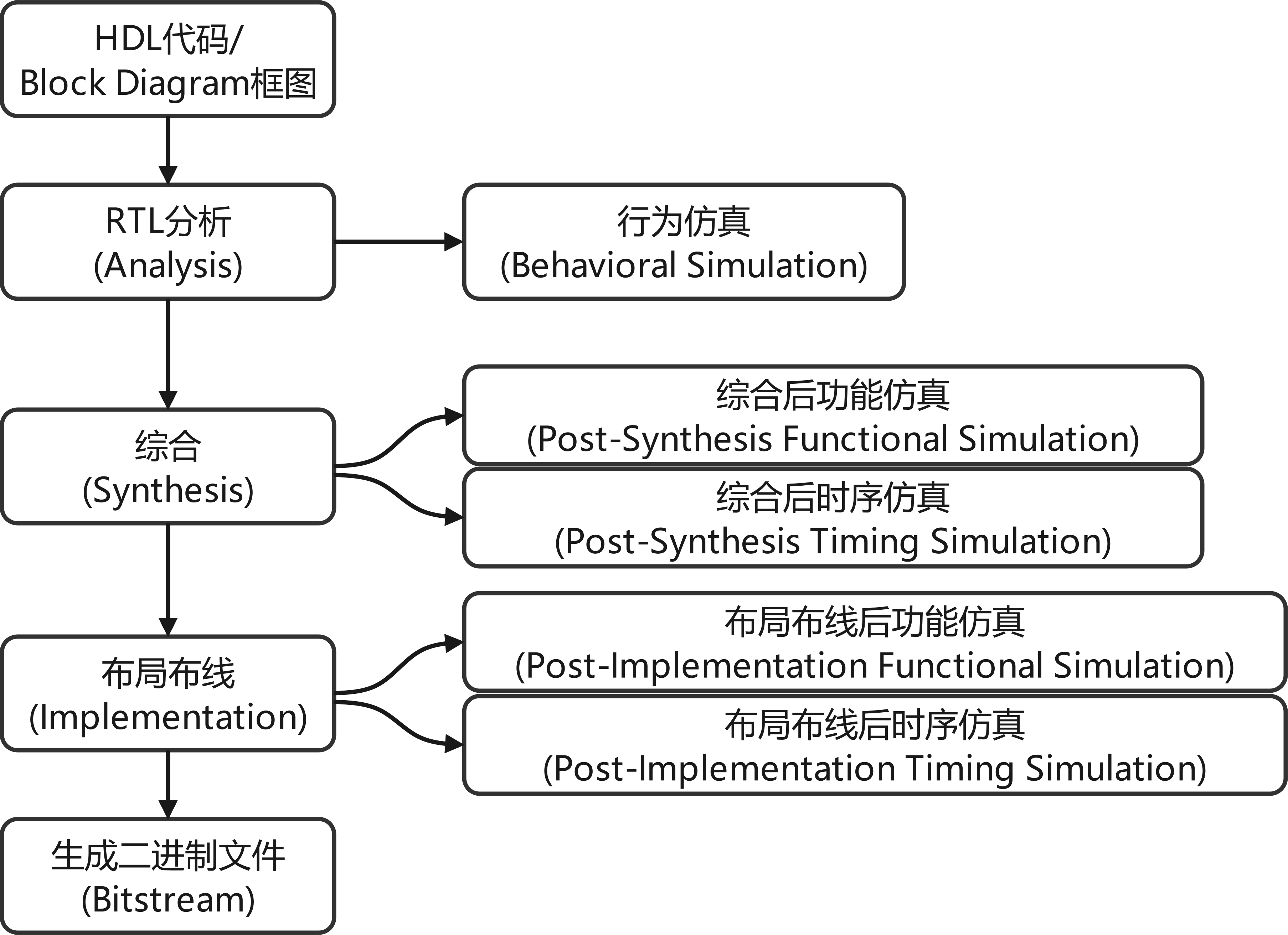

Fpga开发流程可以分为编译,仿真验证,综合,实现,生成比特流文件。记忆这个流程,编译,仿真验证可以看做综合前。

编译这个阶段是将输入的.v文件编译生成中间文件供后续使用,这个阶段你可以验真写的verilog代码是否正确。

综合是根据编译后的中间文件,将其映射为一个个的门级网络,门级网络可以看成是门电路(与或非)还有一些单元(锁相环什么的)组成的这样一种单元。门级网络还有接口,对应的连线。实现的过程就是对连线的布局。

实现,实现的过程是将门级网络将转换为FPGA厂商的底层元件库,再映射为一个个的fpga资源,并将其连线。连线后我们经常会对其生成的时序验证,进行再综合。

生成比特流,生成可以烧录进去fpga的二进制文件。

记忆:综合前,综合,实现,比特流。