产品概述

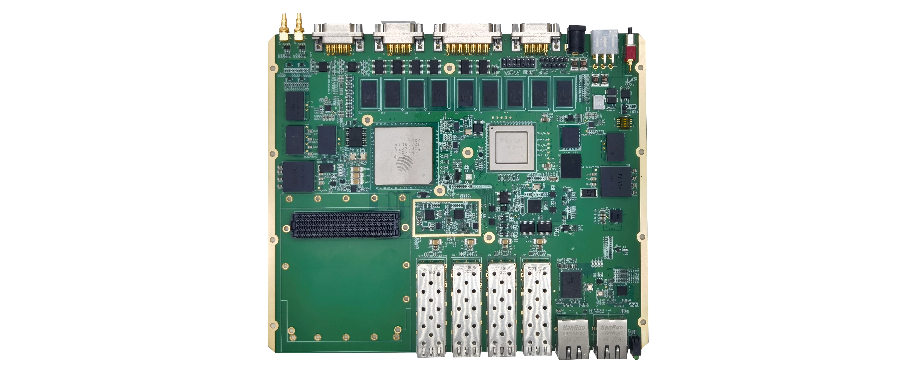

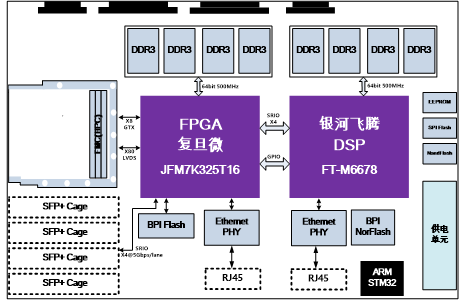

TES600G是一款基于FPGA+DSP协同处理架构的通用高性能实时信号处理平台,该平台采用1片国防科大的银河飞腾多核浮点/定点DSP FT-M6678作为主处理单元,采用1片复旦微的Kintex-7系列FPGA JFM7K325T16作为协处理单元,具有1个FMC子卡接口,具有4路SFP+万兆光纤接口,具有2路RJ45千兆以太网接口,其中1路挂在FPGA上,另外一路挂在DSP上,处理节点之间通过高速串行总线进行互联。

该板卡通过搭配不同的FMC子卡,可广泛应用于软件无线电、雷达信号处理、基带信号处理、无线仿真平台、高速图形图像处理等应用场景。

技术指标

1.处理性能:

-

FPGA(复旦微JFM7K325T)+FT-M6678 DSP协同架构;

-

DSP定点运算:40GMAC/Core*8=320GMAC;

-

DSP浮点运算:20GFLOPs/Core*8=160GFLOPs;

-

FPGA:326080 Logic Cells、16*GTX Transriver;

2. 存储性能:

-

DSP处理节点:2GByte DDR3-1333 SDRAM;

-

DSP处理节点:4GByte Nand Flash;

-

FPGA处理节点:2GByte DDR3 SDRAM;

3. 接口与互联性能:

-

DSP与FPGA:SRIO x4@5Gbps/lane;

-

DSP外挂1个RJ45千兆以太网接口;

-

FPGA外挂1个RJ45千兆以太网接口;

-

FPGA外挂4路SFP+光纤接口;

-

FPGA端:支持32路LVTTL +3.3V IO输出;

-

FPGA端:支持16路LVTTL +3.3V IO输入;

-

FPGA端:支持2路SYNC同步输入接口;

-

FPGA端:支持1路RS422接口;

4. FMC接口

-

支持1个FMC(HPC)接口,符合VITA57.1规范;

-

支持8路GTX高速串行总线;

-

支持84对LVDS接口;

5. 物理与电气特征

-

板卡尺寸:204 x 170mm;

-

产品功耗:max 5A@+12V(±5%);

-

散热方式:风冷/导冷散热;

6. 环境特征

-

工作温度:-40°~﹢85°C;

-

存储温度:-55°~﹢125°C;

-

工作湿度:5%~95%,非凝结;

软件支持

1.可选集成板级软件开发包(BSP):

-

DSP底层接口驱动;

-

FPGA底层接口驱动;

-

板级互联接口驱动(如SRIO等);

-

基于SYS/BIOS的多核处理底层驱动;

2. 可根据客户需求提供定制化算法与系统集成:

应用范围

1.雷达与智能天线、无线基础设施;

2. 宽带RF信号处理;

3. 高速图像处理;自动化测试测量;